# MAGIC – Memristor Aided LoGIC

Shahar Kvatinsky, Student Member, IEEE, Dmitry Belousov, Slavik Liman, Guy Satat, Student Member, Nimrod Wald, Eby G. Friedman, Fellow, IEEE, Avinoam Kolodny, Senior Member, IEEE, and Uri C. Weiser, Fellow, IEEE

*Abstract*— Memristors are passive components with a varying resistance which depends on the previous voltage applied across the device. While memristors are naturally used as memory, memristors can also be used for other applications, including logic circuits. In this paper, a memristor only logic family, MAGIC (Memristor Aided LoGIC), is presented. In each MAGIC logic gate, memristors serve as an input with previously stored data and an additional memristor serves as an output. The topology of a MAGIC NOR gate is similar to the structure of a common memristor-based crossbar memory array. A MAGIC NOR gate can therefore be placed within a memory, providing opportunities for novel non-von Neumann computer architectures. Other MAGIC gates also exist (*e.g.*, AND, OR, NOT, and NAND) and are described in the paper.

## *Index Terms*—Memristive systems, memristor, IMPLY, MAGIC, stateful logic, in-memory computing.

## I. INTRODUCTION

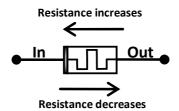

In recent years, the concept of a memristor, originally proposed by Leon Chua in 1971, has generated renewed interest. In [1], Chua proposed a fourth fundamental component in addition to the three already well known fundamental electronic components: the resistor, capacitor, and inductor. In [13], Chua and Kang extended the theory of memristors to memristive systems. Memristors and memristive devices are two-terminal devices, where the resistance of the device is changed by the electrical current, as shown in Figure 1. The resistance of the memristor is bounded by a minimum resistance  $R_{ON}$  and a maximum resistance  $R_{OFF}$ . In this paper, for simplicity, the terms memristor and memristive device are used interchangeably [14].

For almost forty years, the concept of a memristor was just theoretical. In 2008, Hewlett Packard Laboratories [2]

connected the physical phenomenon of resistance switching in TiO2 to memristors. Since 2008, several possible applications of memristors have been presented. Nonvolatile emerging memory technologies, including Resistive RAM (RRAM) and Spin-Transfer Torque Magnetoresistive RAM (STT-MRAM), can be considered as memristors [14]. The primary application of memristors has been memory [3, 16, 22], where the resistance serves to store data. Another interesting and new application is memristor-based logic [4-5, 9-12, 17-18].

Stateful logic, including material implication (IMPLY), as a memristor-based logic gate is presented in [5], [9], [11], [17], [22], [23]. The proposed stateful logic is built within a memristive crossbar array, the most commonly used memristive memory structure (particularly for RRAM). The stored data within the memristors are the input and output of the logic gate. This method, however, requires sequential voltage activation at different locations within the circuit. Furthermore, with IMPLY, the result is stored by one of the inputs and not by a dedicated output memristor. Stateful logic also requires additional circuit components (for example, a controller and an additional resistor within each row of the crossbar), dissipates high power, has high computational complexity, and requires complicated control circuitry.

In this paper, Memristor Aided LoGIC (MAGIC) - a method for memristive-only logic - is presented. This method does not require a complicated structure and enables stable evaluation of the gate function. Stable evaluation is achieved by applying a single voltage pulse at the gateway of the circuit. MAGIC NOR gates can also be fabricated within a crossbar, enabling computing within memory.

## II. OPERATING PRINCIPLE OF MAGIC

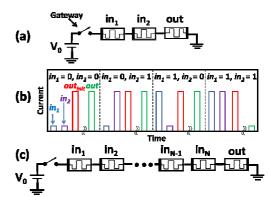

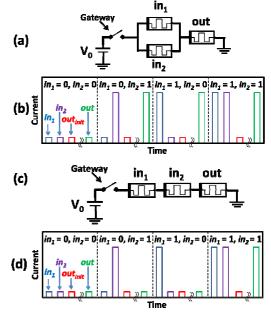

MAGIC requires only memristors within the logic gates. The logical state in a MAGIC gate is represented as a resistance, where the high and low resistances are considered, respectively, as logical zero and one (for simplicity, the resistance of logical zero and logical one is considered, respectively, as  $R_{off}$  and  $R_{on}$ ). The inputs and output of the logic gates are the logical states of the memristors. Unlike an IMPLY logic gate, separate memristors are required for the input and output. The inputs of the MAGIC gates are the initial logical state of the input memristors and the output is the final logical state of the memristor. This concept is demonstrated in Figure 3a for a MAGIC NOR gate, where the initial resistances of memristors *in1* and *in2* are the inputs of the gate

Copyright (c) 2014 IEEE. Personal use of this material is permitted. However, permission to use this material for any other purposes must be obtained from the IEEE by sending an email to pubs-permissions@ieee.org.

Manuscript received 24<sup>nd</sup> April, 2014, revised 1<sup>st</sup> July, 2014. This work was partially supported by Hasso Plattner Institute, by the Advanced Circuit Research Center at the Technion, by the Intel Collaborative Research Institute for Computational Intelligence (ICRI-CI), and by Binational Science Foundation under Grant no. 2012139.

S. Kvatinsky, D. Belousov, S. Liman, A. Kolodny, and U. C. Weiser are with the Department of Electrical Engineering, Technion – Israel Institute of Technology, Haifa 32000, Israel. (S. Kvatinsky corresponding author phone: 972-77-887-1923; fax: 972-4829-5757; e-mail: skva@tx.technion.ac.il).

N. Wald is with Qualcomm Inc., 1 Nahum Het St., Haifa 3190500, Israel. G. Satat is with the MIT Media Lab, Massachusetts Institute of Technology, Cambridge, MA 02139, USA. E. G. Friedman is with the Department of Electrical Engineering and Computer Engineering, University of Rochester, Rochester, NY 14627, USA.

Figure 1. Memristor symbol. The polarity of the memristor is represented by a thick black line. When current flows into the device (the upper arrow), the resistance of the device increases. When current flows out of the device (the lower arrow), the resistance of the device decreases.

and the final resistance of memristor *out* is the output of the gate.

Operation of a MAGIC gate consists of two sequential stages. The first stage initializes the output memristor to a known logical state. In the second stage of operation, a voltage  $V_0$  is applied across the logic gate. While applying  $V_0$ , the voltage across the output memristor depends upon the logical state of the input and output memristors. The nonlinear characteristics of the memristor, namely the threshold currents or voltages [8], are exploited to maintain correct operation. For specific input combinations, the voltage is sufficient to change the logical state of the output memristor, i.e., the memristor voltage/current is greater than the threshold voltage/current, while for other input combinations, the output remains at the initialize state, *i.e.*, the memristor voltage/current is below the threshold current or voltage. Note that in certain cases full switching is not achievable for memristors with a threshold current.

Initialization of the memristors can be achieved in several ways. For example, it is possible to use a similar topology as the circuit used in [19] for configurable memristive analog circuits, as shown in Figure 2. For MAGIC gates within memory (as described in Section III), initialization is achieved as a regular write operation within the memory cells.

In the next section, the basic MAGIC NOR gate is described. Additional MAGIC gates for different Boolean functions based on the MAGIC topology are also available, and described in Section VI.

### III. MAGIC NOR GATE

A two input NOR gate consists of two input memristors (in1, in2) connected in parallel and an additional memristor (out) as the output. A schematic of a two input NOR gate is shown in Figure 3a. The initial execution step includes writing a low resistance into the output memristor (initialization to logical one) and, if necessary, writing the input value into memristors in1 and in2. In the final execution step, the evaluation is achieved by applying a voltage pulse  $V_0$  at the gateway of the logic gate (the gateway as shown in Figure 3a).

The applied voltage produces a current that passes through the circuit and appears at memristor *out*. For the case where both input memristors are logical zero (high resistance), the voltage/current of the output memristor is lower than the memristor threshold voltage/current. Hence, the logical state of the output memristor does not change and remains at logical

Figure 2. Example of placing a memristor into the initialization stage. This example is similar to writing a configurable analog circuit [19]. A different initialization scheme is presented in Section III for MAGIC within memory.

one. For all other input combinations, the voltage/current is greater than the memristor threshold voltage/current. The logical state of the output memristor for these input combinations switches to logical zero. The behavior of the MAGIC NOR gate is shown in Figure 3b.

Assume a memristor with voltage thresholds of  $V_{T,ON}$  and  $V_{T,OFF}$ . For correct circuit behavior, the voltage at the output memristor is lower than  $V_{T,OFF}$  when both inputs are logical zero. For all other input combinations, the voltage across the output memristor should be greater than  $V_{T,OFF}$ . The minimum voltage at the output memristor greater than  $V_{T,OFF}$  is achieved when one input is logical one and the other input is logical zero. Combining the cases where the voltage at the output memristor is above and below the threshold voltage leads to a design constraint on the applied voltage  $V_0$ . The constraint is, assuming  $R_{off} >> R_{on}$ ,

$$2V_{T,OFF} < V_0 < \frac{R_{OFF}}{2R_{ON}} \cdot V_{T,OFF}.$$

(1)

When an input memristor is logical zero, the operation of a MAGIC NOR can be destructive, changing the input to logical one during execution. To eliminate destroying the input, the voltage across the input memristor needs to be below the threshold voltage  $V_{T,ON}$ . The maximum applied voltage for a two-input NOR gate is therefore

$$V_0 < \min\left[\frac{R_{OFF}}{2R_{ON}} \cdot V_{T,OFF}, |V_{T,ON}|\right].$$

<sup>(2)</sup>

Multiple-input (three or more) NOR logic gates can also be produced in a similar manner, as shown in Figure 3c. For  $\chi$ input memristors, the design constraints are

$$\frac{V_{T,OFF}}{R_{ON}} \cdot \left[ R_{ON} + \left( \frac{R_{OFF}}{\chi - 1} \right) \parallel R_{ON} \right] < V_0 < V_{T,OFF} \cdot \left[ 1 + \frac{R_{OFF}}{\chi R_{ON}} \right].$$

(3)

For non-destructive operation of a  $\chi$ -input NOR, the maximum applied voltage is

$$V_0 < \min\left[V_{T,OFF} \cdot \left(1 + \frac{R_{OFF}}{\chi R_{ON}}\right), \left(1 + \frac{\chi R_{ON}}{R_{OFF}}\right) \cdot |V_{T,ON}|\right].$$

(4)

## IV. MAGIC WITHIN A CROSSBAR ARRAY

RRAM commonly utilizes a crossbar structure. The crossbar structure enables dense memory of  $4 F^2$ , where *F* is the feature size. Memristive-only logic gates within a memristive crossbar array reduce power and provide an opportunity for novel non-von Neumann architectures, where the logical operations are

Figure 3. MAGIC NOR. (a) Schematic of a two input NOR gate. The logic gate consists of two input memristors *in1* and *in2*, and an output memristor *out*. During execution, a voltage  $V_{\theta}$  is applied at the gateway of the circuit (marked by an arrow). (b) Simulations of a two input NOR gate for all input combinations. The different curves show the currents read from each memristor prior to execution and after applying  $V_{\theta}$ . (c) Schematic of an N input NOR.

executed within the memory [11]. When performing logic within the memory, the input is the stored data within the memristors and the output is the stored data after execution. Initialization of the input and output is achieved as a regular memory write operation, and sensing the result is achieved as a regular memory read operation.

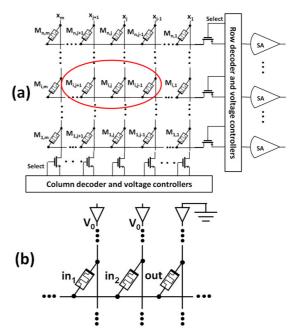

To integrate a memristive-only logic gate within a crossbar array, two requirements need to be satisfied: the structure and connections of the logic gate should be placed within a crossbar array and the logical state of the logic gate is represented as a resistance, as in a memristive memory. A MAGIC NOR gate fulfills both of these requirements. The structure of a memristive crossbar array and a two-input MAGIC NOR gate within a crossbar is shown in Figure 4.

While other memristive stateful logic gates can also be integrated within a memristive crossbar array [11], these logic gates require an additional resistor within each row of the crossbar array. Additionally, unlike the NOR Boolean operation, the IMPLY operation is not logically complete and requires the operation of FALSE (writing a logical zero to a memristor). A comparison between memristive IMPLY and MAGIC is listed in Table 1.

## V. EVALUATION AND DESIGN CONSIDERATIONS FOR A MAGIC NOR GATE

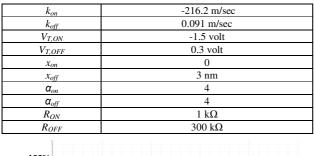

The speed of a MAGIC NOR gate is evaluated in SPICE for a 0.18  $\mu$ m CMOS process. A memristor model, the VTEAM model [20], which extends the TEAM model with a threshold voltage, is used with a Biolek window function [8]. The parameters of the memristors are chosen to produce a switching time of 1 ns for a voltage pulse of 1 volt for RESET and 2 volts for SET, and to fit practical devices, as reported in

Figure 4. MAGIC NOR gate within a crossbar array. (a) Schematic of a memristive crossbar structure. A two input NOR gate is achieved in row *i*, where *in1* and *in2* are, respectively, in columns *j*+1 and *j* and *out* is in column *j*-1, as marked by an oval. (b) Schematic of a two input NOR gate within a crossbar array. The voltage at the gateway  $V_0$  is the applied voltage at columns *j* and *j*+1, while column *j*-1 is connected to ground. Note that the schematic is identical to the figure shown in Figure 3a.

TABLE I. COMPARISON BETWEEN IMPLY AND MAGIC

|                                     | IMPLY [11]             | MAGIC                      |  |

|-------------------------------------|------------------------|----------------------------|--|

| No. of voltages                     | $2(V_{SET}, V_{COND})$ | $1(V_0)$                   |  |

| Separate input and<br>output        | No                     | Yes                        |  |

| Basic functions                     | IMPLY (+ FALSE)        | OR, AND, NOR,<br>NAND, NOT |  |

| No. of memristors for<br>NOR/NAND   | 3 (+ a resistor)       | 3                          |  |

| No. of clock cycles for<br>NOR/NAND | 4                      | 2                          |  |

| Within memory                       | Yes                    | Yes (for NOR)              |  |

| Logically complete                  | Requires FALSE         | Yes (NOR, NAND)            |  |

[21]. The parameters of the circuit simulations are listed in Table 2.

The behavior and speed of a MAGIC NOR gate for different values of  $V_0$  are shown in Figure 5. To evaluate the delay of the logic gate, the slowest input case is considered. The delay of a MAGIC NOR gate is determined from an input combinations of  $\{1,0\}$  or  $\{0,1\}$ .

From (1) and (2),  $V_0$  can vary from 0.6 to 1.5 volts for the parameters listed in Table 2. As shown in Figure 5b, increasing the applied voltage  $V_0$  decreases the delay of the logic gate. For  $V_0$  at 1 volt, the delay of the logic gate is 1.3 ns, an increase of 30% as compared to the switching time of a single memristor.

## VI. ADDITIONAL MAGIC GATES

With the same design principles described in Section II, additional Boolean functions can added to the MAGIC family. The additional MAGIC gates described in this section are not

Figure 5. SPICE simulations of a two input MAGIC NOR gate. (a) Output memristor for different input combinations,  $V_{\theta} = 1$  volt. The delay is evaluated as the time to switch the output memristor to logical zero when one input is logical one and the other input is logical zero (dashed line), and (b) delay for different values of  $V_{\theta}$ .

placed within a crossbar array (except for the NOT gate), but can be used as standalone logic.

Connecting the input memristors in series with the same topology as the MAGIC NOR gate produces a NAND gate, as shown in Figure 6. OR and AND logic gates have a similar structure as, respectively, NOR and NAND, except for the opposite polarity of the output memristor *out*. Unlike NAND and NOR, *out* is initialized to logical zero prior to execution. The schematic and behavior of the OR and AND MAGIC gates are shown in Figure 7. Similar to the MAGIC NOR and NAND gates, multi-input logic gates are also possible for the MAGIC OR and AND gates.

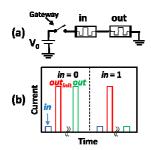

A MAGIC NOT gate (inverter) consists of an input memristor *in* and an output memristor *out*. The memristors are connected in series with an opposite polarity in a complementary memristor structure (or complementary resistive switches) [15], as shown in Figure 8a. In the first stage of execution, the output memristor is initialized to logical one. When applying  $V_0$  at the gateway of the circuit, the voltage divider between *in* and *out* determines whether the resistance of the output memristor changes. For the case where *in* is logical zero, the voltage across *out* is below the threshold voltage and the logical state of *out* remains logical one, as desired. Note that in this case, the voltage at *in* is relatively

Figure 6. MAGIC NAND gate. (a) Schematic of a two input NAND gate. The logic gate consists of two input memristors *in1* and *in2*, and an output memristor *out*. During execution, a voltage  $V_0$  is applied at the gateway of the circuit. (b) Simulation results for a two input NAND gate for all input combinations. The different curves exhibit the currents of each memristor prior to execution and after

applying  $V_{\theta}$ , and (c) schematic of an N input NAND gate.

Figure 7. MAGIC OR and AND gates. The structure of the logic gates is similar to MAGIC NOR and NAND gates. The output memristor *out* is connected with the same polarity as the input memristors, and is initialized to logical zero. (a) Schematic of a two input OR gate. (b) Simulation results for a two input OR gate for all input combinations. (c) Schematic of a two input AND gate. (d) Simulation results for a two input AND gate for all input combinations.

high and the logical state at *in* may therefore be switched to logical zero. Hence, the MAGIC NOT operation can be destructive to the input unless the applied voltage at memristor *in* is below  $V_{T,ON}$ . For the case where *in* is logical one, the voltage across memristor *out* is sufficient to switch the logical state of *out* (greater than the threshold voltage) to logical zero. Simulation results for a NOT gate are shown in Figure 8b. A summary of several MAGIC gates, including the design constraints, is listed in Table 3. For linear memristors and memristors without a threshold voltage (or current), similar design issues as those reported for the IMPLY gate [9, 11] need to be considered (*e.g.*, state drift phenomenon), complicating the design procedure.

Figure 8. MAGIC NOT gate. (a) Schematic of a NOT gate. The logic gate consists of an input memristor *in* and an output memristor *out*, and (b) simulation results for a NOT gate.

### VII. CONCLUSIONS

MAGIC, a novel method for memristor-based logic, is presented in this paper. Five basic logic functions, NOT, AND, NAND, NOR, and OR, use simple connections among memristors, where the number of memristors is equal to the number of inputs plus one additional memristor at the output.

Only one applied voltage controls these logic gates, different than other memristor-based stateful logic. Unlike the IMPLY gate, the input and output in MAGIC are separated, and the output is written to a dedicated memristor. The use of MAGIC NOR gates within a memristive crossbar array can lead to more efficient systems in terms of performance and power consumption, and to novel non-von Neumann architectures.

#### REFERENCES

[1]L. O. Chua, "Memristor – the Missing Circuit Element," *IEEE Transactions on Circuit Theory*, Vol. 18, No. 5, pp. 507-519, September 1971.

[2]D. B. Strukov, G. S. Snider, D. R. Stewart, and R. S. Williams, "The Missing Memristor Found," *Nature*, Vol. 453, pp. 80-83, May 2008.

[3]Y. Ho, G. M. Huang, and P. Li, "Nonvolatile Memristor Memory: Device Characteristics and Design Implications," *Proceedings of the IEEE International Conference on Computer-Aided Design*, pp. 485-490, November 2009.

[4] Q. Xia, W. Robinett, M. W. Cumbie, N. Banerjee, T. J. Cardinalli, J. J. Yang, W. Wu, X. Li, W. M. Tong, D. B. Strukov, G. S. Snider, G. Mederios-Riberio, and R. S. Williams, "Memristor-CMOS Hybrid Integrated Circuits for Reconfigurable Logic," *Nano Letters*, Vol. 9, No. 10, pp. 3640-3645, September 2009.

[5]J. Borghetti, G. S. Snider, P. J. Kuekes, J. J. Yang, D. R. Stewart, and R. S. Williams, "Memristive Switches Enable 'Stateful' Logic Operations via Material Implication," *Nature*, Vol. 464, pp. 873-876, April 2010.

[6]E. Lehtonen, J. H. Poikonen, and M. Laiho, "Two Memristors Suffice to Compute All Boolean Functions," *Electronics Letters*, Vol. 46, No. 3, pp. 239-240, February 2010.

[7]M. D. Pickett, D. B. Strukov, J. L. Borghetti, J. J. Yang, G. S. Snider, D.

R. Stewart, and R. S. Williams, "Switching Dynamics in Titanium Dioxide Memristive Devices," *Journal of Applied Physics*, Vol. 106, 074508, October 2009.

[8]S. Kvatinsky, E. G. Friedman, A. Kolodny and U. C. Weiser, "TEAM: ThrEshold Adaptive Memristor Model," *IEEE Transactions on Circuits and Systems I: Regular Papers*, Vol. 60, No. 1, pp. 211-221, January 2013.

[9]S. Kvatinsky, E. G. Friedman, A. Kolodny and U. C. Weiser, "Memristorbased IMPLY Logic Gate Design Procedure," *Proceedings of the IEEE International Conference on Computer Design*, pp. 142-147, October 2011.

[10] S. Kvatinsky, N. Wald, G. Satat, E. G. Friedman, A. Kolodny, and U. C. Weiser, "MRL – Memristor Ratioed Logic for Hybrid CMOS-Memristor Circuits," *IEEE Transactions on Nanotechnology* (in review).

[11] S. Kvatinsky, E. G. Friedman, A. Kolodny, and U. C. Weiser, "Memristor-based Material Implication (IMPLY) Logic: Design Principles and Methodologies," *IEEE Transactions on Very Large Scale Integration* (VLSI) (in press).

[12] S. Kvatinsky, N. Wald, G. Satat, E. G. Friedman, A. Kolodny, and U. C. Weiser, "MRL – Memristor Ratioed Logic," *Proceedings of the International Cellular Nanoscale Networks and their Applications*, pp. 1-6, August 2012.

[13] L. O. Chua and S. M. Kang, "Memristive Devices and Systems," *Proceedings of the IEEE*, Vol. 64, No. 2, pp. 209-223, February 1976.

[14] L. O. Chua, "Resistance Switching Memories are Memristors," *Applied Physics A: Materials Science & Processing*, Vol. 102, No. 4, pp. 765-783, March 2011.

[15] E. Linn, R. Rosezin, C. Kügeler, and R. Waser, "Complementary Resistive Switches for Passive Nanocrossbar Memories," *Nature Materials*, Vol. 9, No. 5, pp. 403–406, April 2010.

[16] R. Patel, S. Kvatinsky, E. G. Friedman, and A. Kolodny, "Multistate Register Based on Resistive RAM," *IEEE Transactions on Very Large Scale Integration (VLSI)* (in press).

[17] E. Lehtonen and M. Laiho, "Stateful Implication Logic with Memristors," *Proceedings of the IEEE/ACM International Symposium on Nanoscale Architectures*, pp. 33-36, July 2009.

[18] Y. Levy, J. Bruk, Y. Cassuto, E. G. Friedman, A. Kolodny, E. Yaacobi, and S. Kvatinsky, "Logic Operation in Memory Using a Memristive Akers Array," *Microelectronics Journal* (in press).

[19] Y. V. Pershin and M. Di Ventra, "Practical Approach to Programmable Analog Circuits with Memristors," *IEEE Transactions on Circuits and Systems I: Regular Papers*, Vol. 57, No. 8, pp. 1857-1864, August 2010.

[20] S. Kvatinsky, M. Ramadan, E. G. Friedman, and A. Kolodny, "VTEAM – A General Model for Voltage Controlled Memristors," *CCIT Technical Report #856*, April 2014.

[21] J. J. Yang, D. B. Strukov, and D. R. Stewart, "Memristive Devices for Computing," *Nature Nanotechnology*, Vol. 8, pp. 13-24, January 2013.

[22] K. Kyosun S. Shin, and S.-M.S. Kang, "Field Programmable Stateful Logic Array," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, Vol. 30, No. 12, pp. 1800-1813, December 2011.

[23] E. Lehtonen, J. H. Poikonen, and M. Laiho, "Applications and Limitations of Memristive Implication Logic," *Proceedings of the International Workshop on Cellular Nanoscale Networks and Their Applications (CNNA)*, pp.1-6, August 2012.

TABLE III. SUMMARY OF MAGIC GATES

| Function | Design Constraints                                                                                                   | Design Constraints – Multiple Inputs                                                                                                                                                                                                                                          | Within<br>Crossbar? |

|----------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| NOR      | $2V_{T,OFF} < V_0 < \min\left[\frac{R_{OFF}}{2R_{ON}} \cdot V_{T,OFF}, \left V_{T,ON}\right \right]$                 | $\frac{V_{T,OFF}}{R_{ON}} \cdot \left[ R_{ON} + \left( \frac{R_{OFF}}{\chi - 1} \right) \parallel R_{ON} \right] < V_0 < \min \left[ V_{T,OFF} \cdot \left( 1 + \frac{R_{OFF}}{\chi R_{ON}} \right), \left( 1 + \frac{\chi R_{ON}}{R_{OFF}} \right) \cdot  V_{T,ON}  \right]$ | Yes                 |

| NAND     | $3V_{T,OFF} < V_0 < \min\left[\left V_{T,ON}\right , \left(2 + \frac{R_{OFF}}{R_{ON}}\right) \cdot V_{T,OFF}\right]$ | $\left(\chi+1\right) \cdot V_{T,OFF} < V_0 < \min\left[\left V_{T,ON}\right  \cdot \left(1+\frac{\chi R_{ON}}{R_{OFF}}\right), \left(\chi+\frac{R_{OFF}}{R_{ON}}\right) \cdot V_{T,OFF}\right]$                                                                               | No                  |

| OR       | $V_{T,ON} < V_0 < 1.5 V_{T,ON}$                                                                                      | $V_{T,ON} < V_0 < \left(1 + \frac{1}{\chi}\right) V_{T,ON}$                                                                                                                                                                                                                   | No                  |

| AND      | $V_{T,ON} < V_0 < 2V_{T,ON}$                                                                                         | $\left(1 + \frac{R_{ON}}{R_{OFF}}\chi\right)V_{T,ON} < V_0 < \left(2 + \frac{R_{ON}}{R_{OFF}}(\chi - 1)\right)V_{T,ON}$                                                                                                                                                       | No                  |

| NOT      | $2V_{T,OFF} < V_0 < \frac{R_{OFF}}{R_{ON}} \cdot \min\left(V_{T,OFF},  V_{T,ON} \right)$                             | _                                                                                                                                                                                                                                                                             | Yes                 |