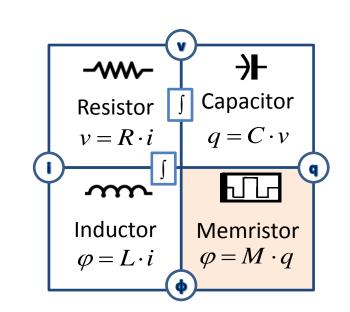

# Logic Design with Memristors

#### Shahar Kvatinsky

Technion – Israel Institute of Technology ACRC Workshop March 2012

#### **Memristors are Useful for Logic**

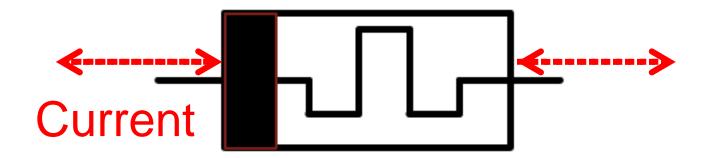

- Two terminal resistive device

- Not only memory

- This talk is about

#### memristor-based logic circuits

Chua, "Memristor – The Missing Circuit Element," *IEEE Trans.*, 1971 Chua and Kang, "Memristive Devices and Systems," *Proceedings of the IEEE*, 1976

#### **Logic with Memristors**

- Memristors as a building block

- Memristor can:

- Store an **input** value

- Store an **output** value

- Perform logic operation

- Act as a state register

(latch, Flip-Flop)

- Act as a configurable switch

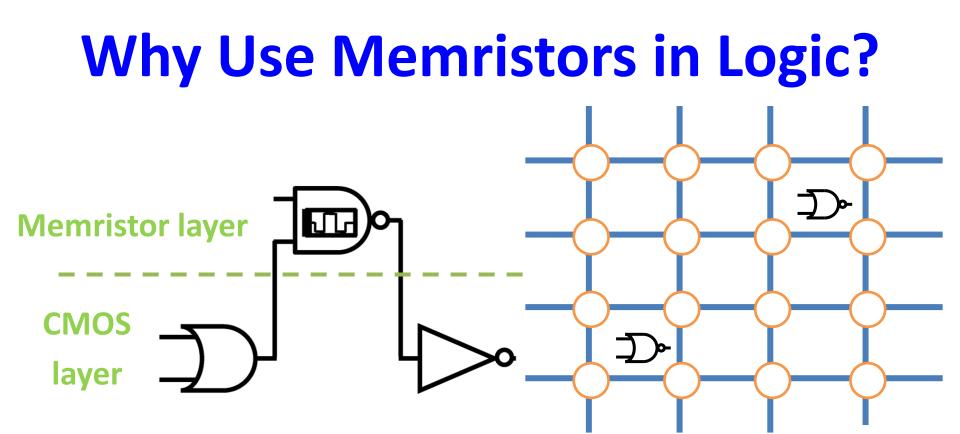

Integrating memristors with standard logic Save die area More logic on die

Logic inside the memory

Beyond Von-Neumann Flexible

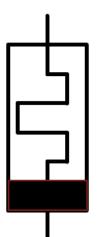

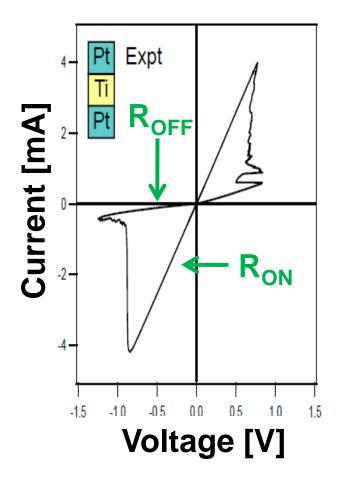

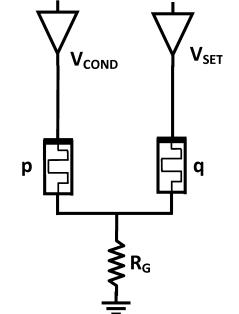

#### **Memristor Polarity**

#### **Decrease resistance**

#### Outline

- Motivation / Why logic with memristors?

- Integrating memristor with standard logic

- Memristor-based logic inside the memory:

- IMPLY logic Gate

- Memristor Aided LoGIC (MAGIC)

- Design methodology

- Conclusions

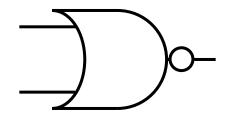

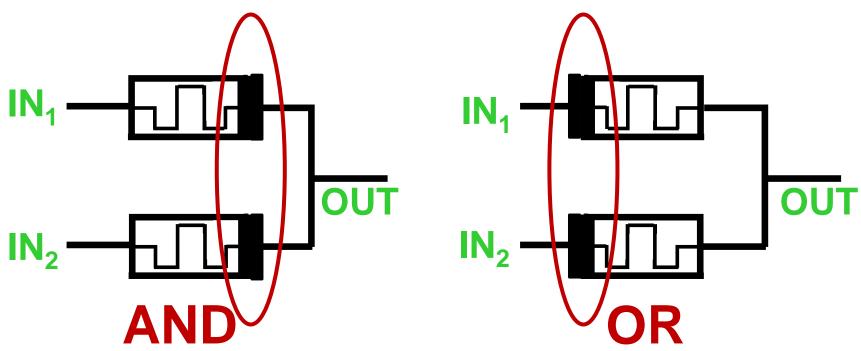

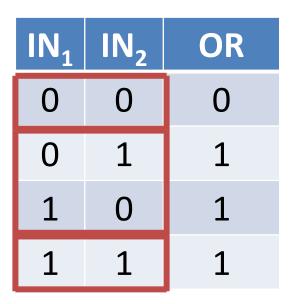

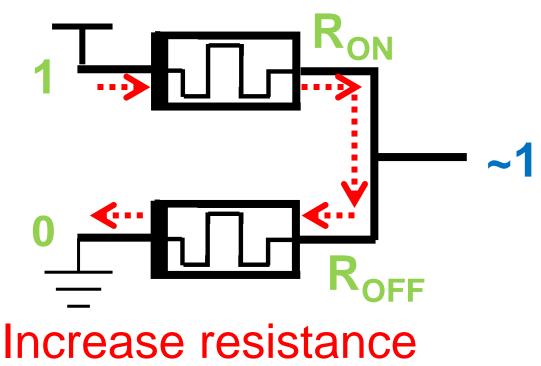

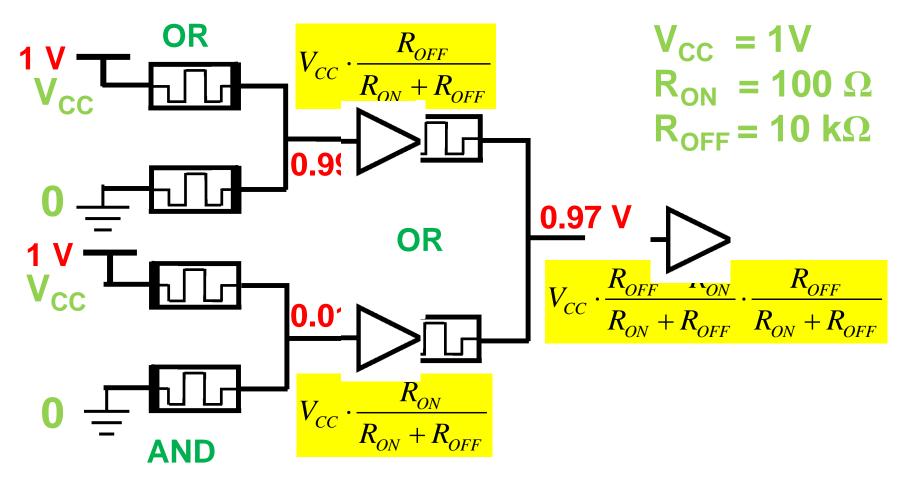

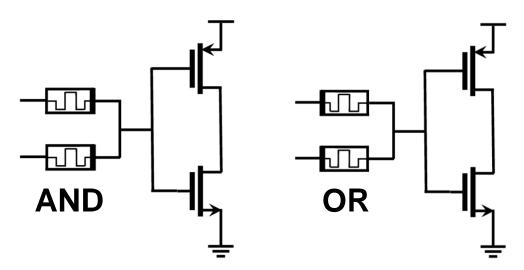

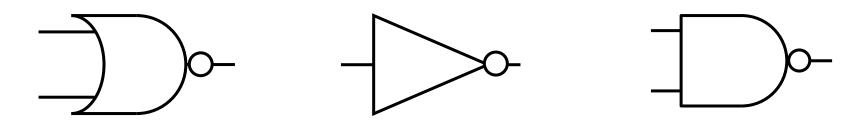

#### AND and OR (Eshraghian 2011)

- Voltage as logic state

- Memristors only as computational elements

7

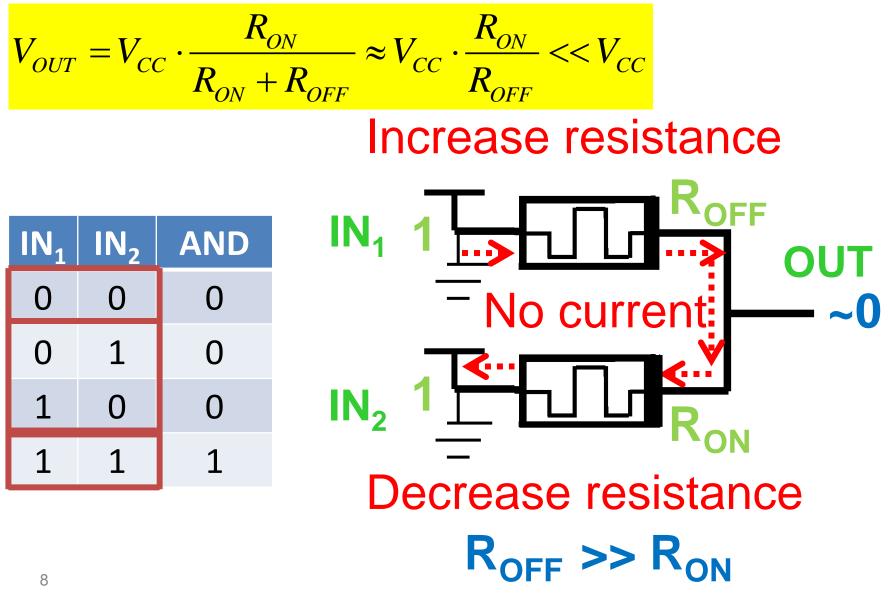

#### **AND Operation**

K. Eshraghian, course notes on "Memristive Circuits and Systems," Technion, June 2011

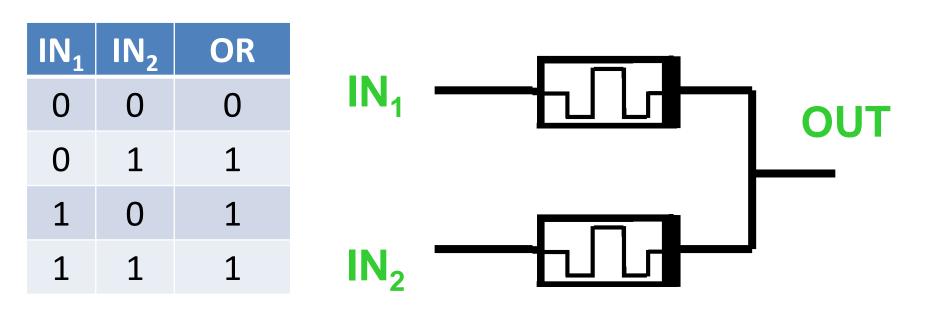

#### **AND to OR**

9

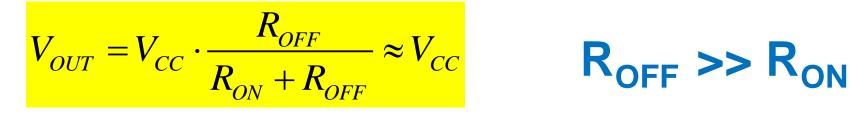

#### **OR Operation**

#### Decrease resistance

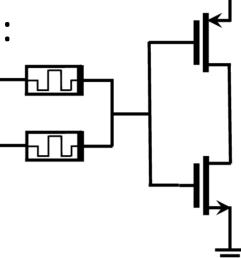

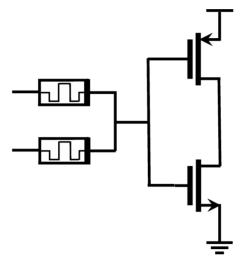

#### **Need for Amplification**

• Chain of memristor-based logic gates

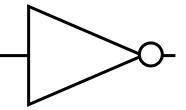

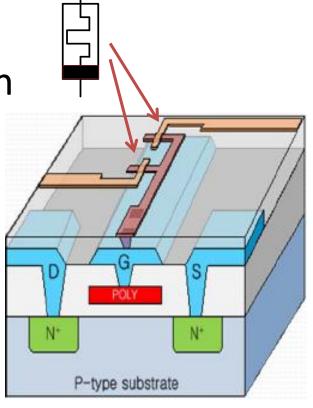

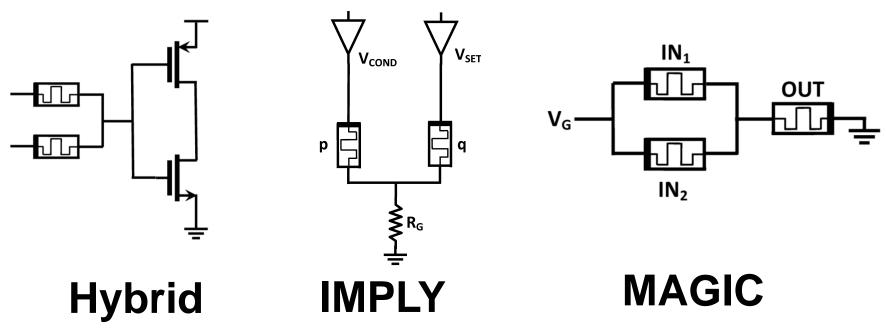

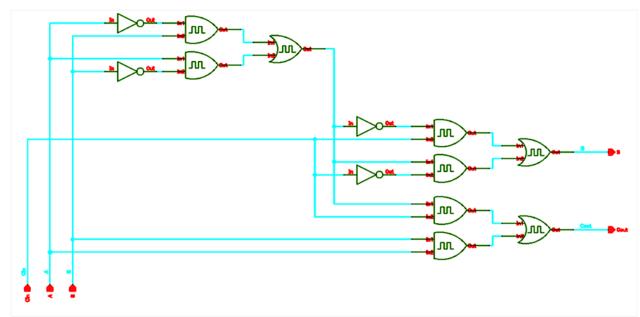

#### **CMOS Compatibility**

- Memristors can be fabricated with CMOS

- Input/output are voltages as in standard

CMOS logic

- Amplify signal signal restoration

K. Eshradhian, course notes on "Memristive Circuits and Systems," Technion, June 2011 J. Borghetti etl al, "A Hybrid Nanomemristor/Transistor Logic Circuit Capable of Self-Programming," PNAS 2008

# Integrating Memristor with Standard Logic - Summary

- Good for integration with standard logic

- Signal restoration through CMOS

- Save die area: 2 transistor 2 memristor

- CMOS memristor layer transition:

—

vias, power and area overhead

#### Outline

- Motivation / Why logic with memristors?

- Integrating memristor with standard logic

- Memristor-based logic inside the memory:

IMPLY logic Gate

- Memristor Aided LoGIC (MAGIC)

- Design methodology

- Conclusions

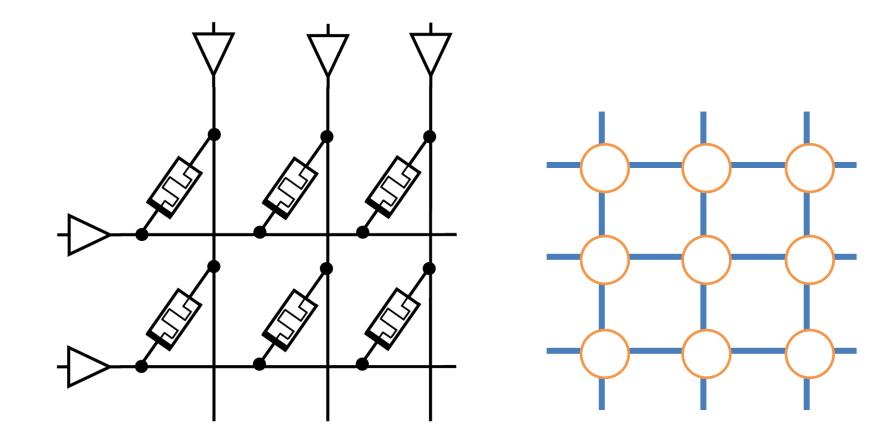

#### **Logic Inside the Memory**

• Based on memristor-based crossbar memory

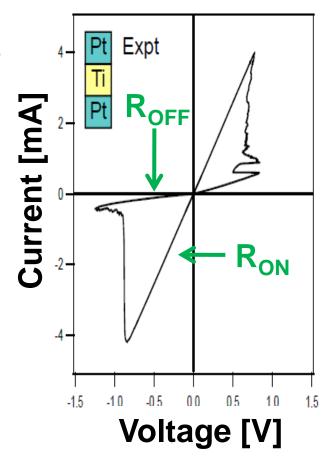

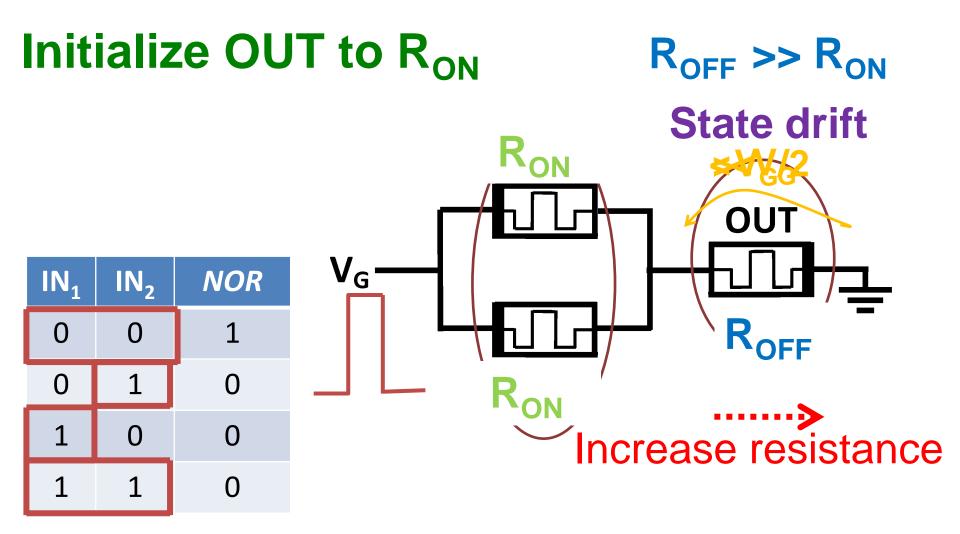

#### **Logical State as Resistance**

- $R_{ON} \rightarrow logical$  '1',  $R_{OFF} \rightarrow logical$  '0'

- The input of the logic gate is the memristor-based cells value

- The result is stored into the memory

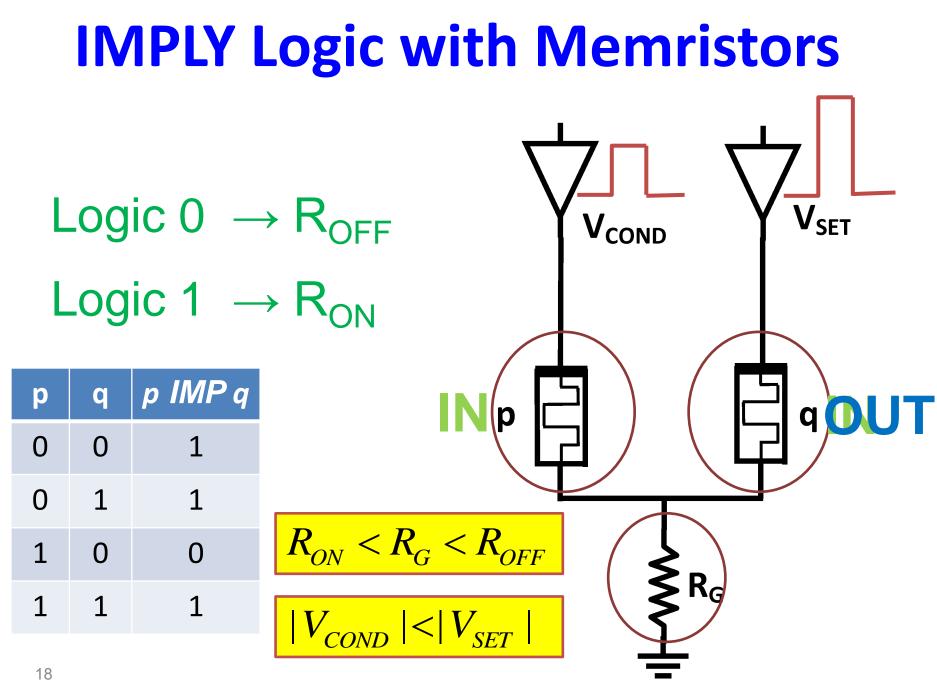

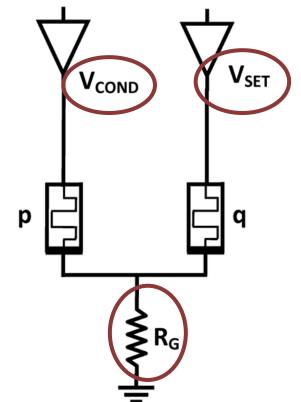

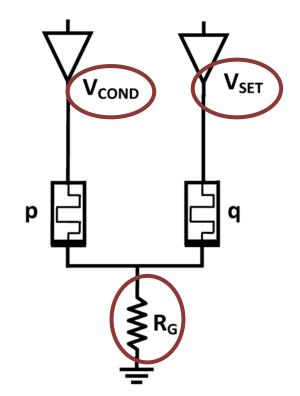

#### **IMPLY Function**

One of the elementary 2 input Boolean functions

Truth Table

| р | q | p IMP q |  |  |  |  |

|---|---|---------|--|--|--|--|

| 0 | 0 | 1       |  |  |  |  |

| 0 | 1 | 1       |  |  |  |  |

| 1 | 0 | 0       |  |  |  |  |

| 1 | 1 | 1       |  |  |  |  |

$p \rightarrow q$ If p then q

#### IMPLY + FALSE Complete logic

J. Borghetti et al, "Memristive Switches Enable 'Stateful' Logic Operation via Material Implication," Nature, 2010

S. Kvatinsky et al, "Memristor-based IMPLY Logic Design Procedure," ICCD, 2011

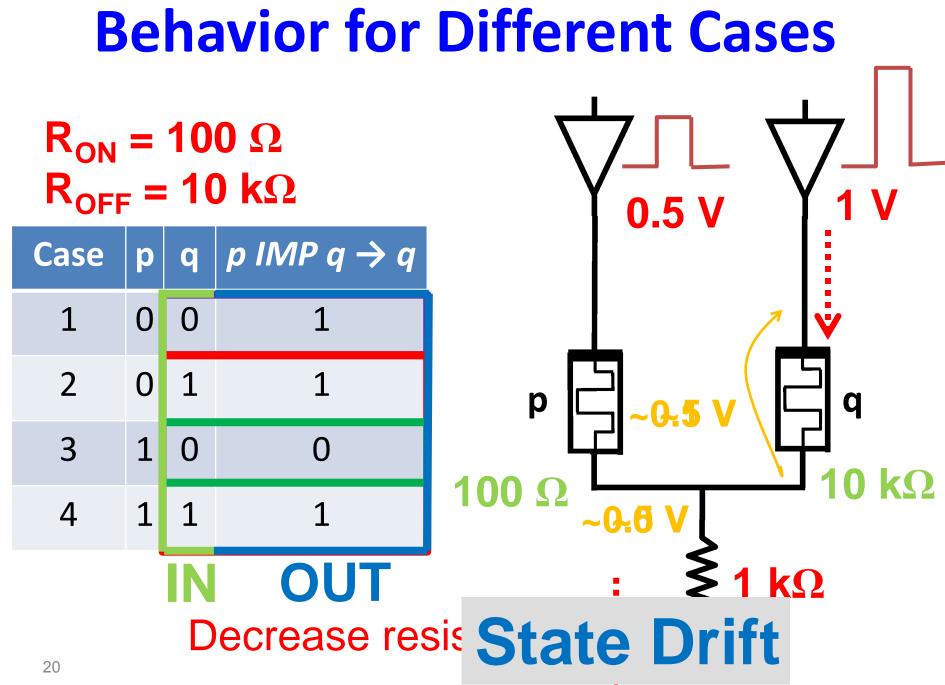

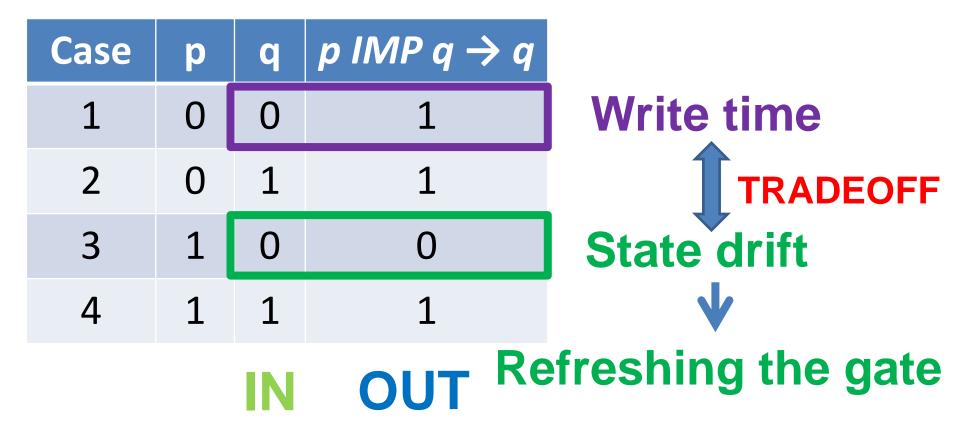

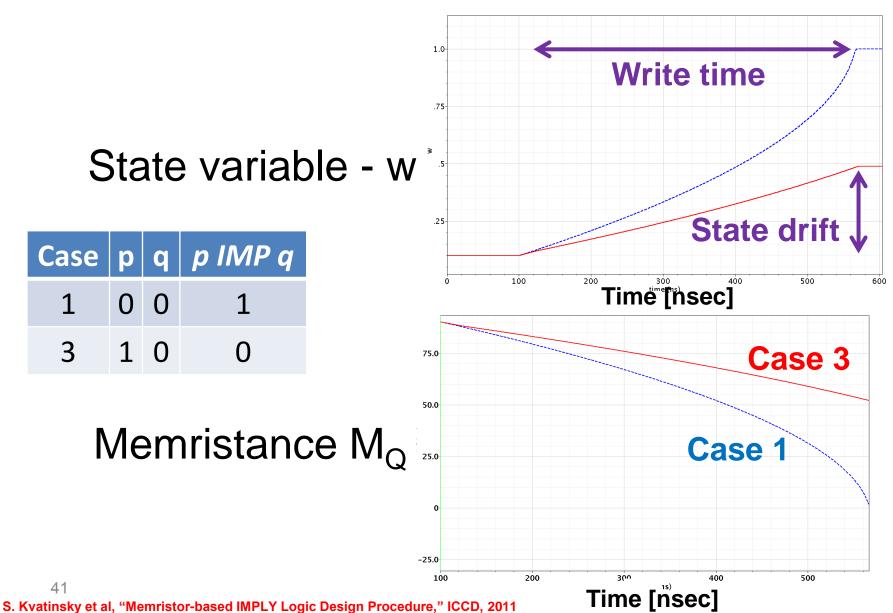

#### Performance and Robustness Tradeoff

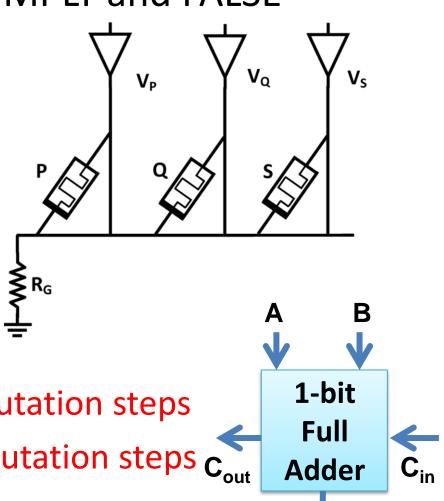

#### **General Functions with IMPLY**

- Sequential operation of IMPLY and FALSE

- NAND:

- Step 1 FALSE(S)

- Step 2 P IMPLY S

- Step 3 Q IMPLY S

- 1- bit Full Adder

- Naive approach: 89 computation steps

- Parallel approach: 5 computation steps Cout

#### **IMPLY Summary**

- Performance and robustness tradeoff

- Need for refresh because of state drift

- For general Boolean function needs many

computation stages:

- Slow

- Complex controller

- Power consumption

#### Outline

- Motivation / Why logic with memristors?

- Integrating memristor with standard logic

- Memristor-based logic inside the memory:

IMPLY logic Gate

- Memristor Aided LoGIC (MAGIC)

- Design methodology

- Conclusions

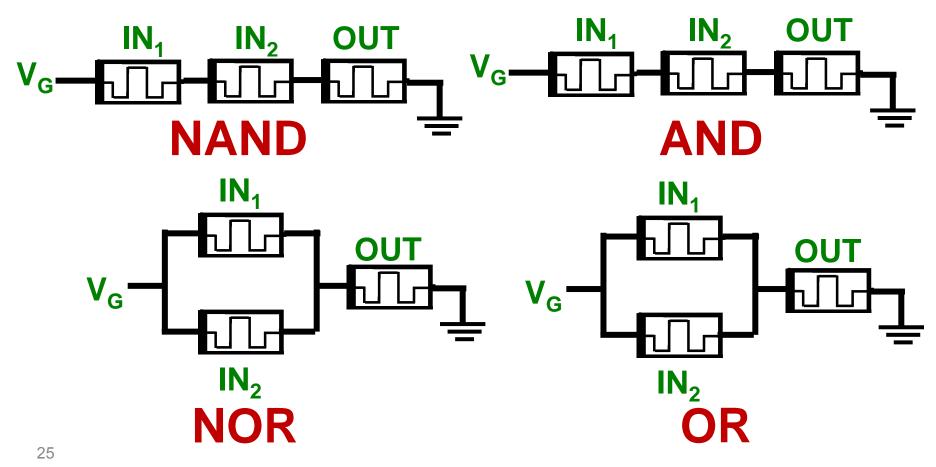

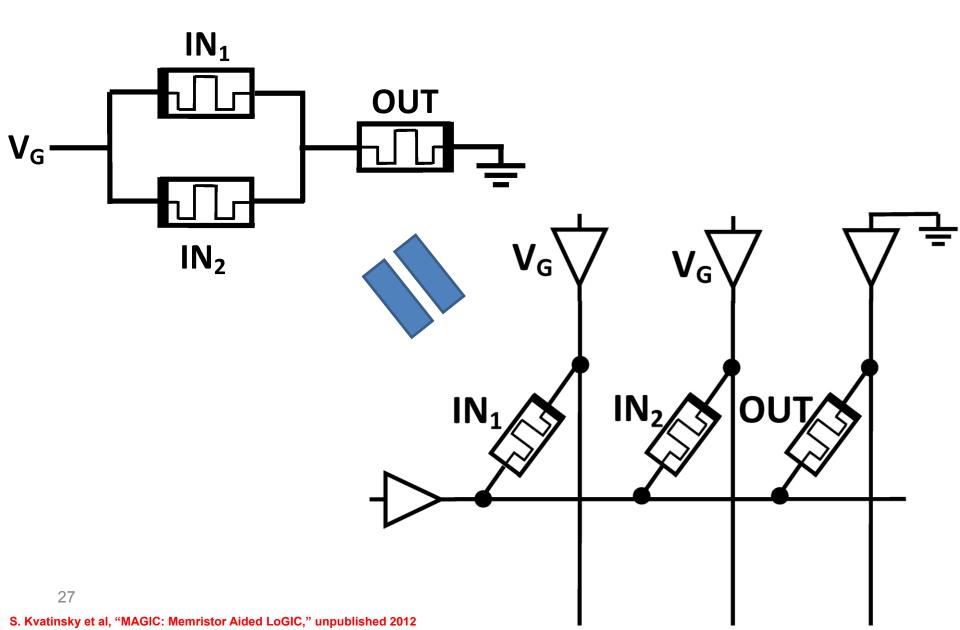

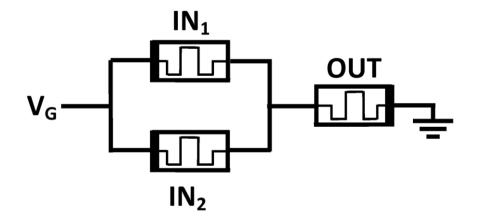

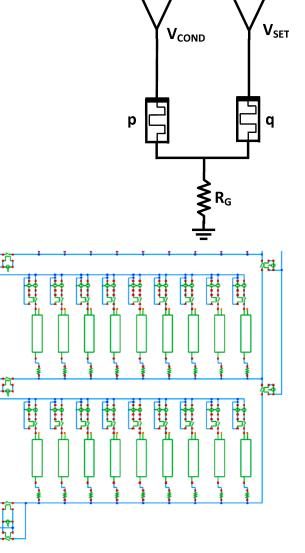

#### MAGIC – Memristor Aided LoGIC

- One applied voltage V<sub>G</sub>

- Separate input and output memristors

#### **MAGIC NOR**

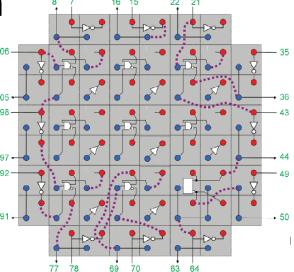

#### **MAGIC NOR in Crossbar**

#### **MAGIC - Summary**

- Good for logic inside the memory

- Separate input and output memristors

- Easy and intuitive

- State drift phenomenon noise margin issues

#### Outline

- Motivation / Why logic with memristors?

- Integrating memristor with standard logic

- Memristor-based logic inside the memory:

- IMPLY logic Gate

- Memristor Aided LoGIC (MAGIC)

- Design methodology

- Conclusions

#### **Need Design Methodology**

- Decide which family to use

- Determine proper circuit parameters

- $-R_{G}$ ?

- Voltage levels? V<sub>COND</sub>? V<sub>SET</sub>?

- Logic gate delay?

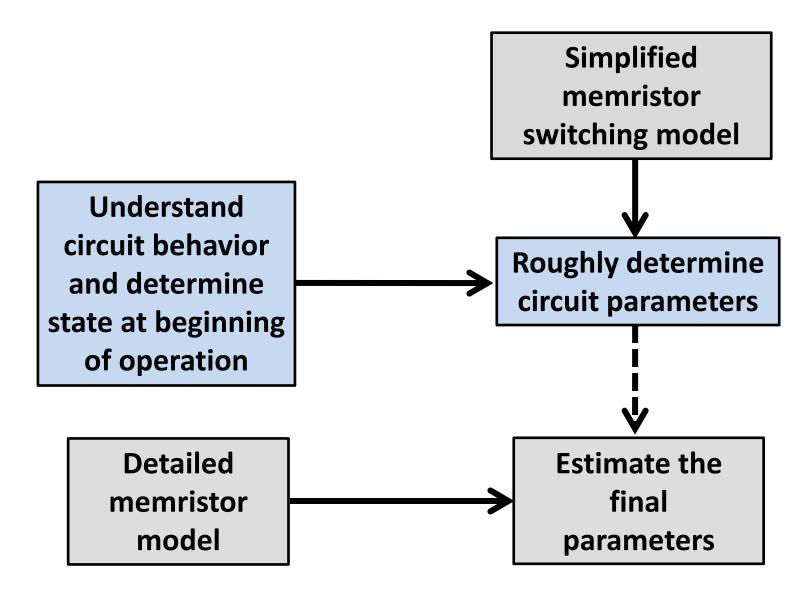

### **Developing Design Methodology**

- IMPLY logic gate design methodology (ICCD 2011)

- Developing a complete design methodology

- General design constraints:

- Power

- Area

- Performance

- Specific design constraints

#### Outline

- Motivation / Why logic with memristors?

- Integrating memristor with standard logic

- Memristor-based logic inside the memory:

- IMPLY logic Gate

- Memristor Aided LoGIC (MAGIC)

- Design methodology

- Conclusions

#### **Logic with Memristors**

#### Many issues – huge opportunities! Reduce die area More computation on die

**Beyond Von-Neumann architecture**

# Thanks!

# BACKUP

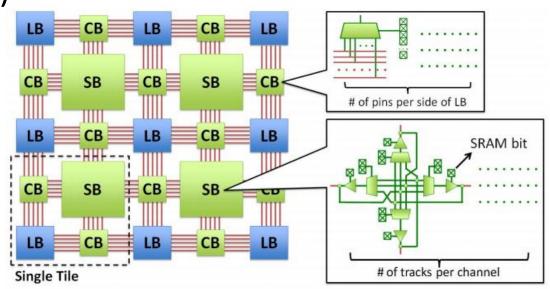

#### **Conventional FPGA**

- FPGA power consumption:

- 90% SRAM (routing)

- 10% computing

LB – logic blocks

38

- CB connection blocks

- SB switching blocks

Cong and Xiao, "mrFPGA: A Novel FPGA Architecture with Memristor-Based Reconfiguration," NANOARCH 2011

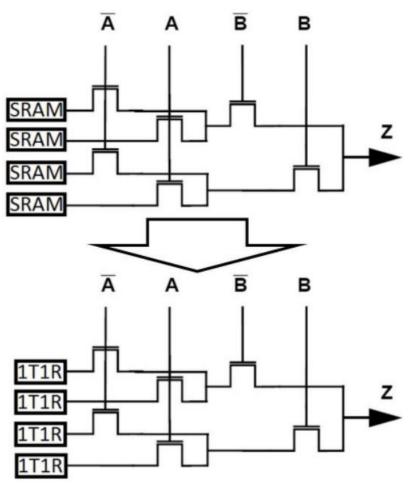

#### **Switching and Connection Blocks**

- Memristor as configurable switch

- 1.6X better power consumption

- 2.28X better critical path delay

#### **Logic Block**

• LUT with 1T1M instead of SRAM

#### **Linear Ion Drift Model**

#### **Design Flow**

S. Kvatinsky et al, "Memristor-based IMPLY Logic Design Procedure," ICCD, 2011

42

#### 8-bit Full Adder Example

|              | A B                                    |                | C_out | S | C_in | В | Α  |

|--------------|----------------------------------------|----------------|-------|---|------|---|----|

|              | <b>1</b>                               |                | 0     | 0 | 0    | 0 | 0  |

|              |                                        |                | 0     | 1 | 1    | 0 | 0  |

| $\leftarrow$ | 1-bit Full                             |                | 0     | 1 | 0    | 1 | 0  |

| C_in         | Adder                                  | C_out          | 1     | 0 | 1    | 1 | 0  |

|              |                                        |                | 0     | 1 | 0    | 0 | 1  |

|              | S                                      |                | 1     | 0 | 1    | 0 | 1  |

|              | $\oplus B \oplus C_{in}$               | $S = A \Theta$ | 1     | 0 | 0    | 1 | 1  |

|              |                                        |                | 1     | 1 | 1    | 1 | 1  |

| $A \oplus B$ | $A \cdot B + C_{in} \cdot (A \cdot B)$ | $C_{out} = R$  |       |   |      |   | 43 |

#### **General Design Constraints**

- Power consumption

- Performance gate delay time

- Area number of memristors (and transistors)

#### **IMPLY Design Constraints**

- Power determine  $V_{SET}$  and  $V_{COND}$

- Performance minimize computation steps

- Area minimize number of memristors

#### 8-bit IMPLY Full Adder

- Naive approach:

- 89 computation steps per bit

- 3 memristors per bit + 5 memristors

- Improved approach:

- Parallel computing, scheduling

- 5 computation steps per bit (+18)

- 9 memristors per bit (72 total)

# Hybrid CMOS-Memristor Design Constraints

Minimize number of CMOS-memristor

transitions (number of vias)

Solution: use inverter (or buffers) only when

necessary

### 8-bit Hybrid CMOS-Memristor Full Adder

- 144 memristors

- Area and vias is depended on memristor behavior:

- Linear memristor 160 transistors, 80 vias

- Nonlinear memristor- 256 memristors, 96 vias

#### **Design Summary**

|                           | IMPLY                       | Hybrid CMOS-<br>Memristor               |

|---------------------------|-----------------------------|-----------------------------------------|

| Performance               | Sequential<br>58 steps      | 6X faster<br>1 step                     |

| Area –<br>memristor layer | 72 memristors<br>2X smaller | 144 memristors                          |

| Area – CMOS<br>layer      | Controller                  | Memristor behavior<br>80-96 transistors |

| Power                     | Dynamic<br>power            | Static and dynamic<br>More power        |