# Memristor-Based IMPLY Logic Gate Design Procedure

Shahar Kvatinsky, Eby G. Friedman,\* Avinoam Kolodny, and Uri C. Weiser

Technion – Israel Institute of Technology \*University of Rochester ICCD 2011

#### Logic Design with Memristors

- Our contributions:

- Methodology for logic design with memristors

- Performance robustness tradeoff

- Simplified memristor models

- Demonstration that the widely used memristor model is impractical

#### Outline

- Memristors

- IMPLY logic Gate

- Design procedure

- Conclusions and future work

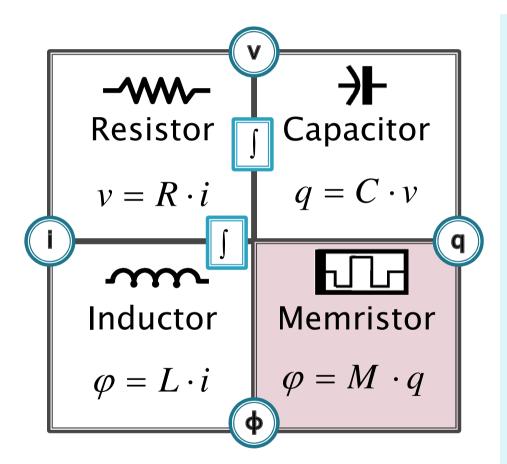

#### **Memristors**

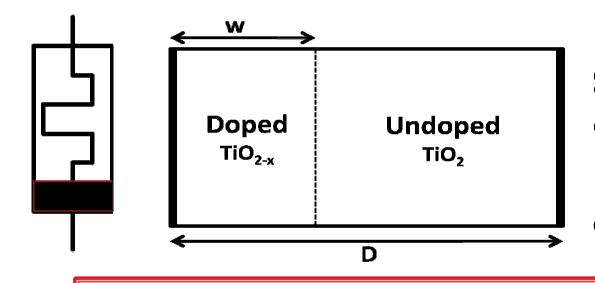

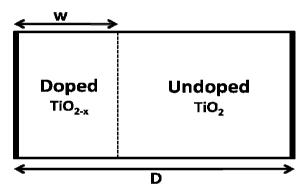

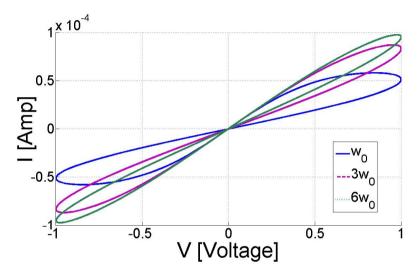

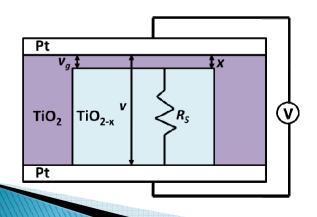

#### **Practical Memristors**

2008 Hewlett Packard

$$M(q) = R_{OFF} \left( 1 - \frac{\mu_{v} R_{ON}}{D^2} q(t) \right)$$

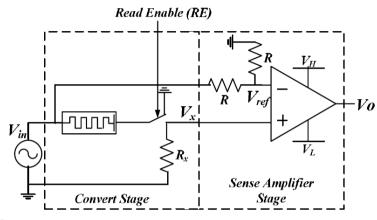

## Memristor-Based Applications

- Memory

- Analog circuits

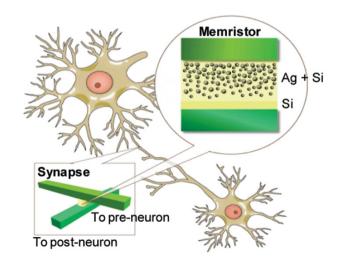

- Neuromorphic systems

- Logic

## Logic with Memristors

- ►  $R_{ON}$  → logic '1',  $R_{OFF}$  → logic '0'

- Memristors as the primary building block

- Memristor can be:

- Input

- Output

- Computational logic element

- Latch

#### Outline

- Memristors

- ▶ IMPLY logic gate

- Design procedure

- Conclusions and future work

### **IMPLY Logic Gate**

| р | q | p IMP q |

|---|---|---------|

| 0 | 0 | 1       |

| 0 | 1 | 1       |

| 1 | 0 | 0       |

| 1 | 1 | 1       |

$$p \longrightarrow p \rightarrow q$$

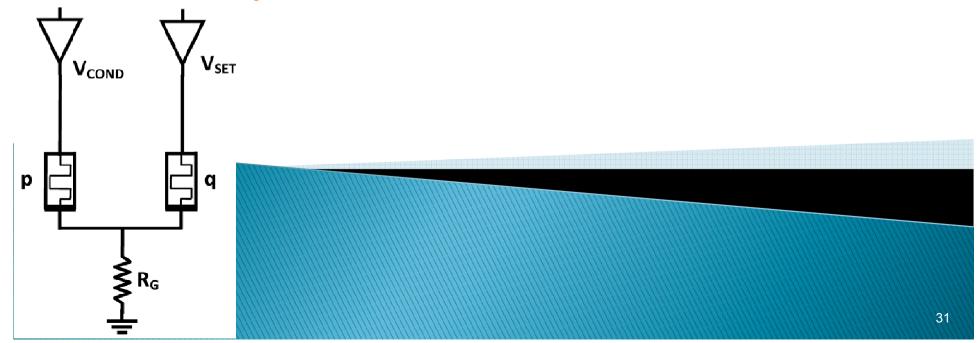

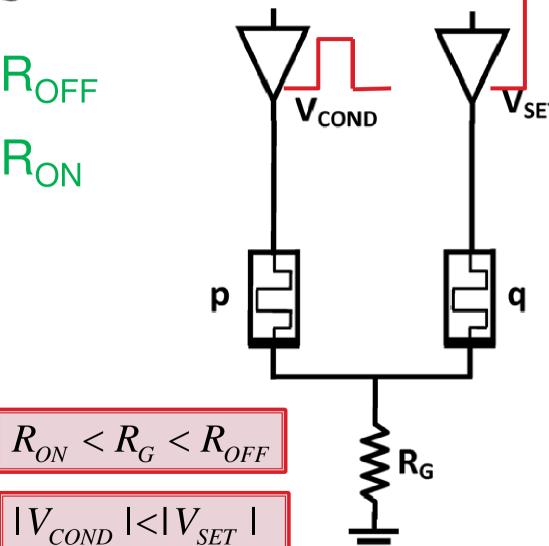

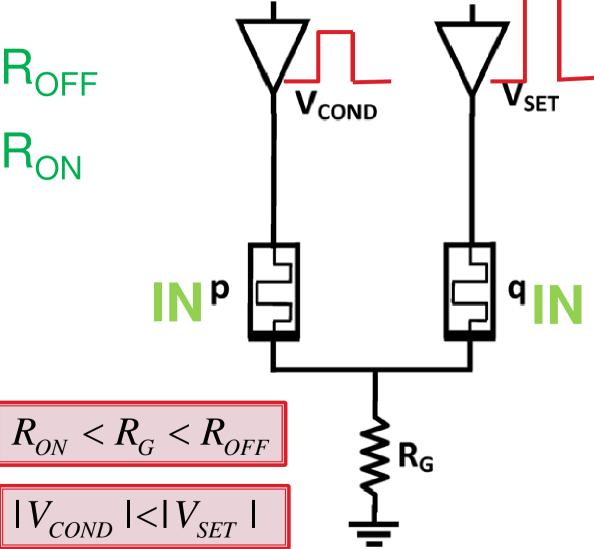

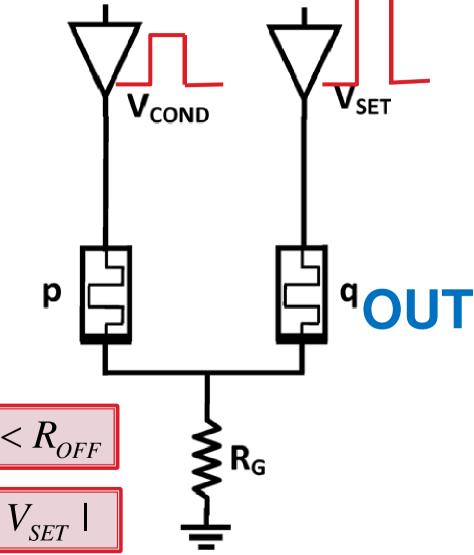

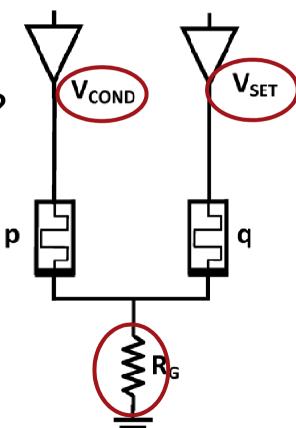

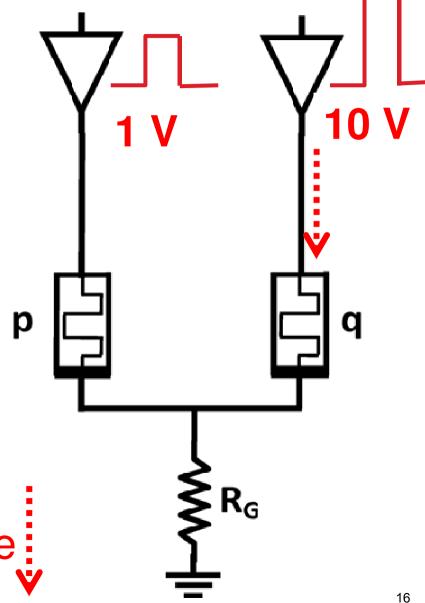

IMPLY Logic with Memristors

$Logic \ 0 \ \to R_{OFF}$

Logic 1  $\rightarrow R_{ON}$

| p | q | p IMP q |

|---|---|---------|

| 0 | 0 | 1       |

| 0 | 1 | 1       |

| 1 | 0 | 0       |

| 1 | 1 | 1       |

Logic 1  $\rightarrow R_{ON}$

| p | q | p IMP q |

|---|---|---------|

| 0 | 0 | 1       |

| 0 | 1 | 1       |

| 1 | 0 | 0       |

| 1 | 1 | 1       |

IMPLY Logic with Memristors

$Logic \ 0 \ \to R_{OFF}$

Logic 1  $\rightarrow R_{ON}$

| p | q | p IMP q |

|---|---|---------|

| 0 | 0 | 1       |

| 0 | 1 | 1       |

| 1 | 0 | 0       |

| 1 | 1 | 1       |

$$|V_{COND}| < |V_{SET}|$$

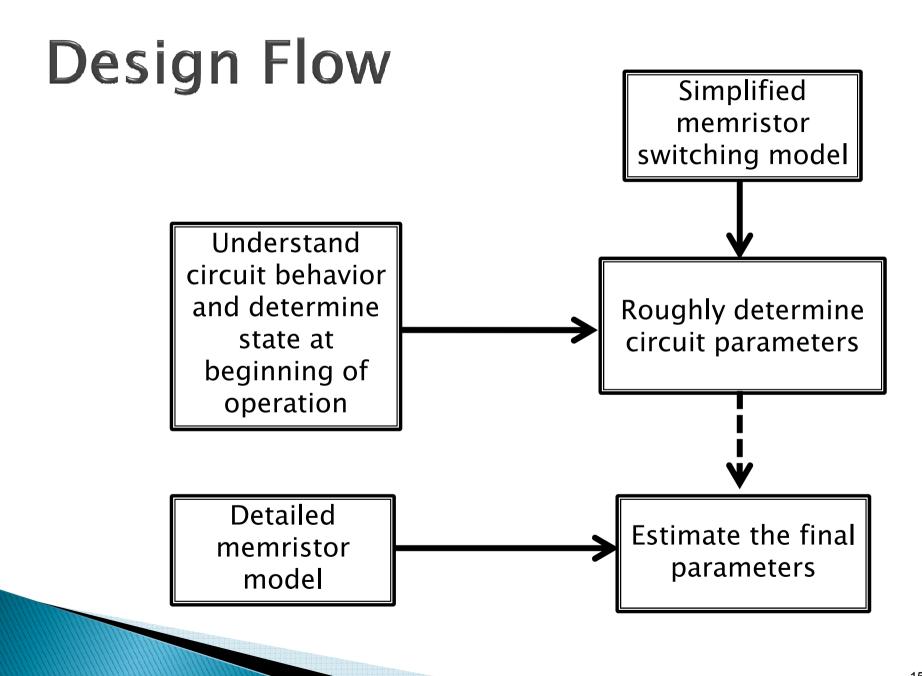

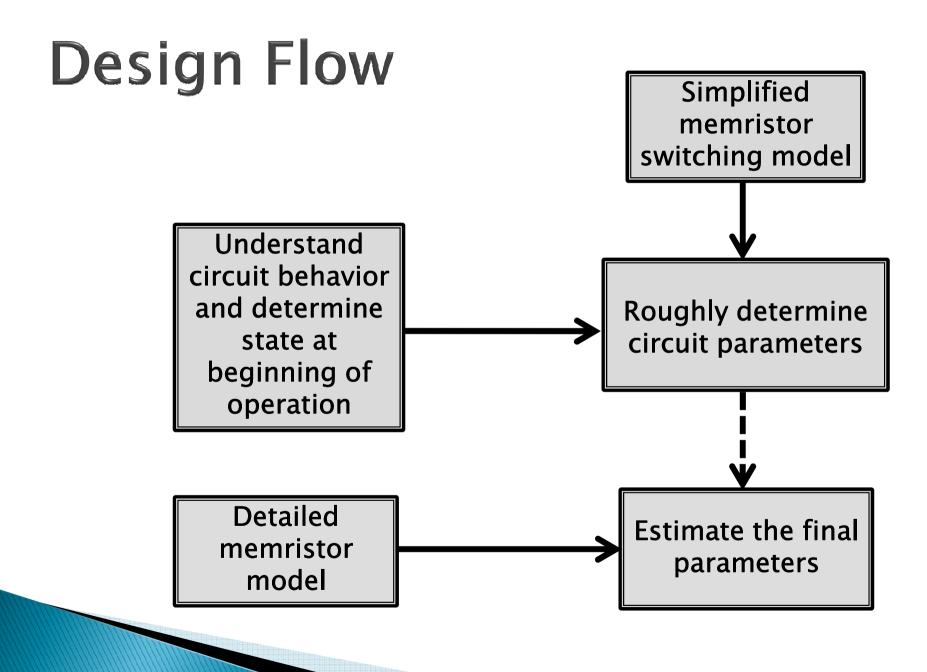

# Need Design Methodology

Determine proper circuit parameters

• Voltage levels? V<sub>COND</sub>? V<sub>SET</sub>?

• Logic gate delay?

#### Outline

- Memristors

- IMPLY logic gate

- Design procedure

- Conclusions and future work

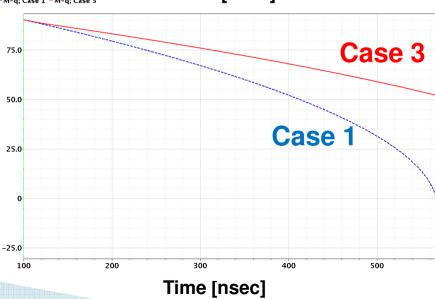

#### Behavior for Different Input

Cases

$$R_{ON} = 1 \Omega$$

$R_{OFF} = 1 M\Omega$

| Case | p | q | $p IMP q \rightarrow q$ |

|------|---|---|-------------------------|

| 1    | 0 | 0 | 1                       |

| 2    | 0 | 1 | 1                       |

| 3    | 1 | 0 | 0                       |

| 4    | 1 | 1 | 1                       |

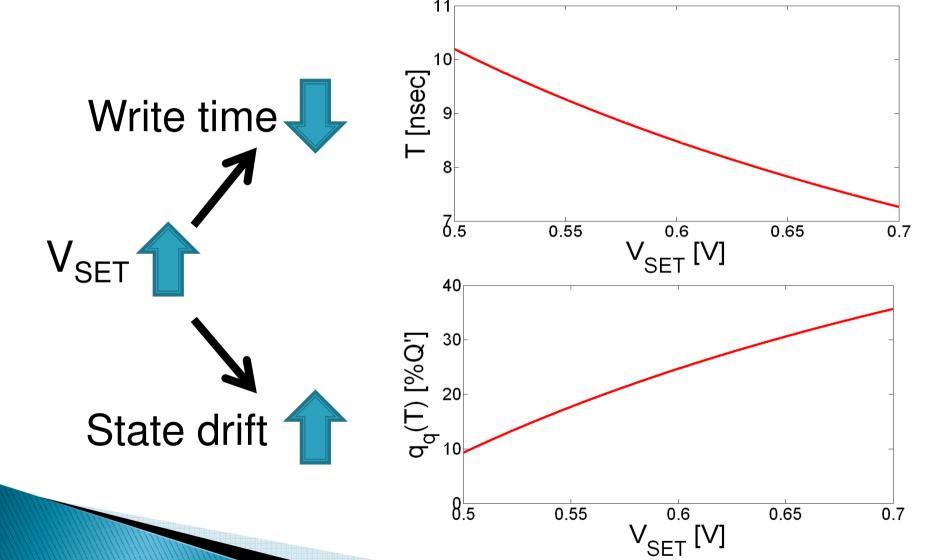

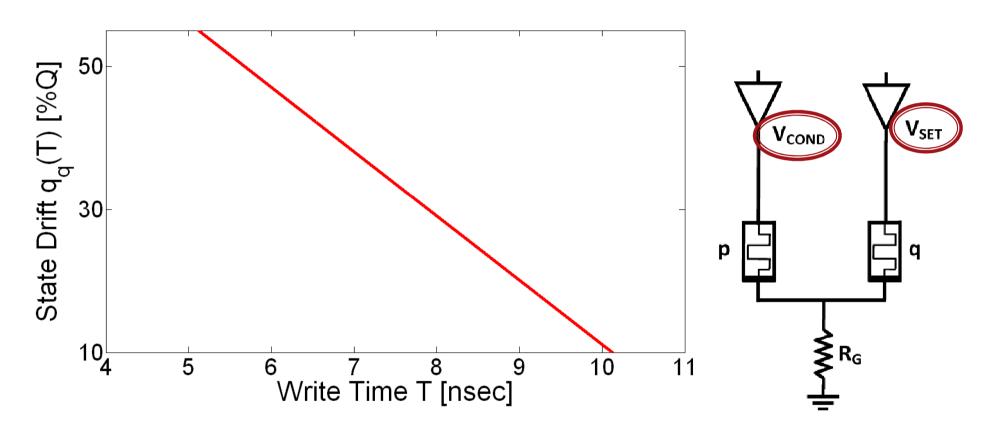

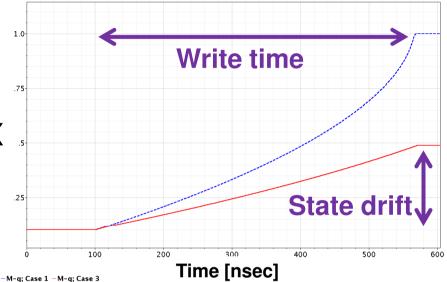

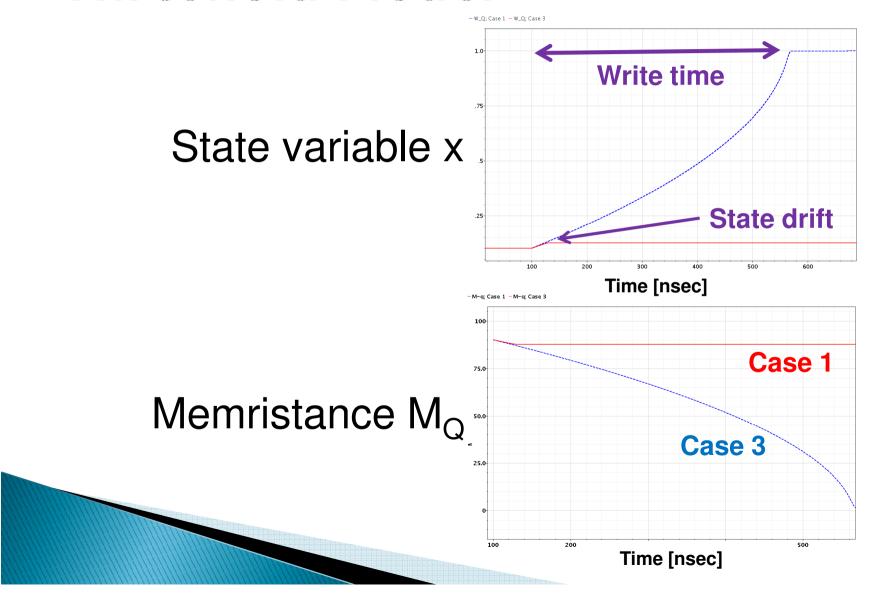

# Performance and Robustness Tradeoff

|             | $p IMP q \rightarrow q$ | q | p | Case |

|-------------|-------------------------|---|---|------|

| Write time  | 1                       | 0 | 0 | 1    |

| TRADEOF     | 1                       | 1 | 0 | 2    |

| State drift | 0                       | 0 | 1 | 3    |

| <b>V</b>    | 1                       | 1 | 1 | 4    |

N OUT Refreshing the gate

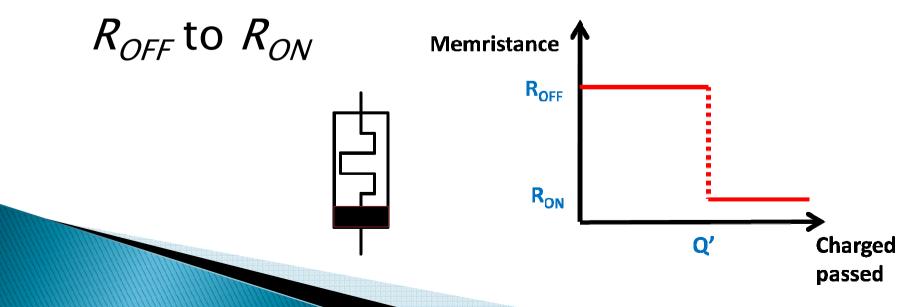

# Binary Memristance Model

- For computing write time and state drift

- Two memristance states  $R_{ON}$  and  $R_{OFF}$

- Charge of Q' must flow to switch from

#### Write Time and State Drift

# Performance and Robustness Tradeoff

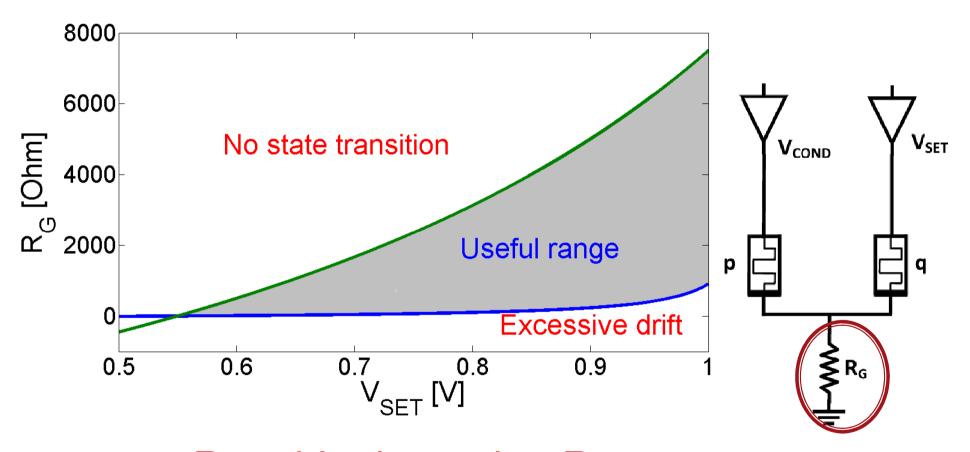

Roughly determine voltage levels

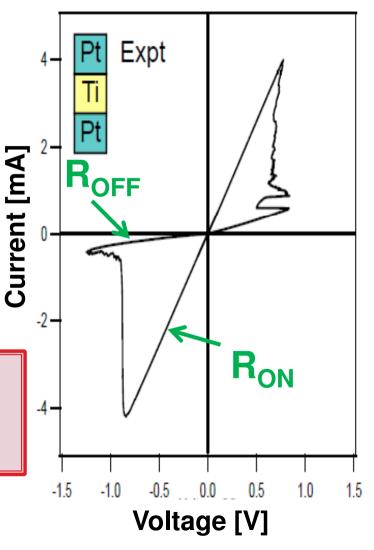

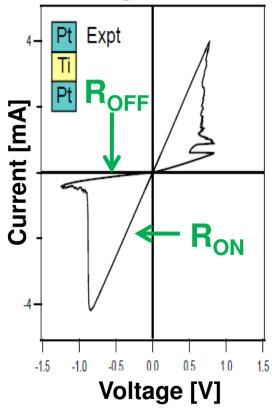

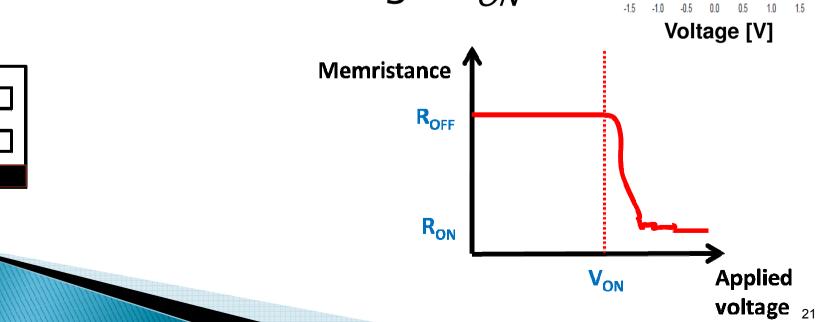

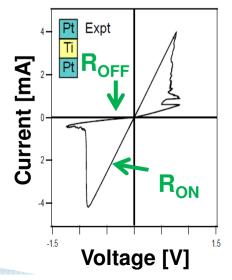

#### Fixed Threshold Model

- For choosing the value of R<sub>G</sub>

- Nonlinear behavior

- Fixed threshold voltage  $V_{ON}$

Expt

RON

Current [mA]

# R<sub>G</sub> Design Constraints

Roughly determine R<sub>G</sub>

#### **Detailed Memristor Models**

Linear ion drift model

Nonlinear ion drift with threshold model

#### Linear Ion Drift Model

| Case | p | q | p IMP q |

|------|---|---|---------|

| 1    | 0 | 0 | 1       |

| 3    | 1 | 0 | 0       |

# Nonlinear Ion Drift with Threshold Model

#### Outline

- Memristors

- IMPLY logic gate

- Design procedure

- Conclusion and future work

# Summary – Logic Design with Memristors

- IMPLY logic gate was presented and analyzed

- We offered procedures for designing

IMPLY logic gates with memristors and organized it into a design flow

#### Conclusions

- Performance and robustness tradeoff

- Need for refresh because of state drift

- Widely used linear ion drift memristor model is incompatible for logic design

# Conclusions – Beyond This Talk

- More in the paper a detailed design example

- Future work complete design

methodology for memristor–based

logic

# Thanks!

http://memristor.shorturl.com