Adi Hayon 12/03/2018

## The PULP Processor Parallel-Ultra-Low-Power

## Parallel Ultra Low Power (PULP)

- The project started in 2013 by Luca Benini

- A collaboration between University of Bologna and ETH Zurich

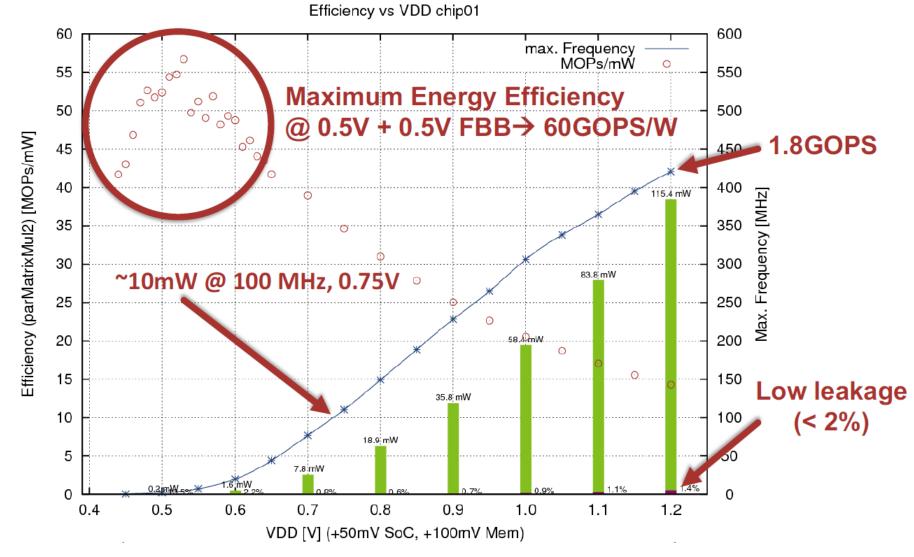

- The key goal is: How to get the highest performance for the ENERGY consumed in a computing system.

# Energy efficiency is the key driver in the PULP project

## **PULP Goals**

- Concentrating on **programmable** systems

- Cannot have custom hardware, need to be scalable

- Making the system accessible to application developers

- Scalable over a wide operating range

- Work just as well when processing 0.001 GOPS as 1000 GOPS

- Don't waste idle energy

- Eliminate sources where cores and systems are idly wasting energy

- Take advantage of heterogeneous acceleration

- Allow an architecture where accelerators can be added efficiently

## Why is Open Hardware Different than Open Software?

- From gnu.org www site:

- http://www.gnu.org/philosophy/free-hardware-designs.html

- **Software** is the operational part of a device that can be copied and changed in a computer

- Hardware is the operational part that can't be.

- You can not produce HW directly, you need

- manufacturing plants

- know-how

- and volume

to be able to manufacture HW with reasonable cost.

# Open Hardware is a necessity, not an ideological crusade

- The way we design ICs has changed, big part is now infrastructure

- Processors, peripherals, memory subsystems are now considered infrastructure

- Very few (if any) groups design complete IC from scratch

- High quality building blocks (IP) needed

# Open Hardware is a necessity, not an ideological crusade

- The way we design ICs has changed, big part is now infrastructure

- Processors, peripherals, memory subsystems are now considered infrastructure

- Very few (if any) groups design complete IC from scratch

- High quality building blocks (IP) needed

- We need an easy and fast way to collaborate with people

- Currently complicated agreements have to be made between all partners

- In many cases, too difficult for academia and SMEs

# Open Hardware is a necessity, not an ideological crusade

- The way we design ICs has changed, big part is now infrastructure

- Processors, peripherals, memory subsystems are now considered infrastructure

- Very few (if any) groups design complete IC from scratch

- High quality building blocks (IP) needed

- We need an easy and fast way to collaborate with people

- Currently complicated agreements have to be made between all partners

- In many cases, too difficult for academia and SMEs

- Hardware is a critical for security, we need to ensure it is secure

- Being able to see what is really inside will improve security

- Having a way to design open HW, will not prevent people from keeping secrets.

# Current HW only supports security through obscurity

- Systems are built on hardware blocks where you do not know what exactly is inside

- Open standards have proven themselves in SW. Why should HW be any different?

- If you really want, you can still 'obscure' HW, but open HW gives you a choice!

- Many bugs, features with unintentional consequences are hiding inside HW

- Open HW will allow a larger community to verify building blocks

- Better verification, more reliable hardware

## Open Hardware

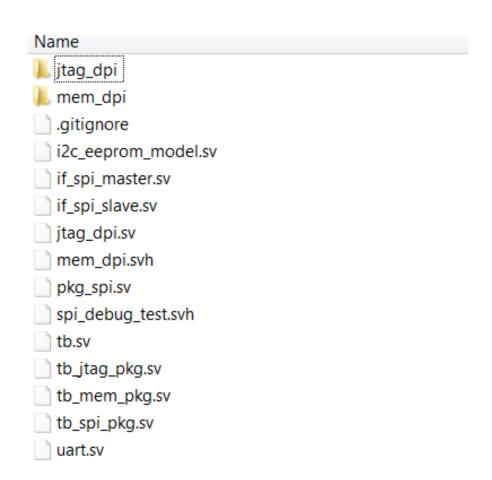

- ZIP file from github includes:

- RTL Code

```

Name

components

includes

apb_mock_uart.sv

axi2apb_wrap.sv

axi mem if SP wrap.sv

axi_node_intf_wrap.sv

axi_slice_wrap.sv

axi_spi_slave_wrap.sv

boot_code.sv

boot_rom_wrap.sv

clk_rst_gen.sv

core2axi_wrap.sv

core_region.sv

dp_ram_wrap.sv

instr_ram_wrap.sv

periph_bus_wrap.sv

peripherals.sv

pulpino_top.sv

ram mux.sv

random_stalls.sv

sp_ram_wrap.sv

```

```

`include "axi bus.sy"

`include "debug bus.sy"

`define AXI_ADDR_WIDTH

32

`define AXI DATA WIDTH

32

`define AXI ID MASTER WIDTH

`define AXI ID SLAVE WIDTH

`define AXI USER WIDTH

module pulpino top

# (

parameter USE ZERO RISCY

parameter RISCY RV32F

parameter ZERO RV32M

parameter ZERO RV32E

// Clock and Reset

input logic

clk /*verilator clocker*/,

input logic

rst n,

input logic

clk sel i,

input logic

clk standalone i,

input logic

testmode i,

input logic

fetch enable i,

scan enable i,

input logic

//SPI Slave

spi clk i /*verilator clocker*/,

input logic

input logic

spi cs i /*verilator clocker*/,

spi mode o,

output logic [1:0]

spi sdo0 o,

output logic

```

- ZIP file from github includes:

- RTL Code

- Testbench

- ZIP file from github includes:

- RTL Code

- Testbench

- Example C code

```

// Copyright 2017 ETH Zurich and University of Bologna.

// Copyright and related rights are licensed under the Solderpad Hardware

// License, Version 0.51 (the "License"); you may not use this file except in

// compliance with the License. You may obtain a copy of the License at

// http://solderpad.org/licenses/SHL-0.51. Unless required by applicable law

// or agreed to in writing, software, hardware and materials distributed under

// this License is distributed on an "AS IS" BASIS, WITHOUT WARRANTIES OR

// CONDITIONS OF ANY KIND, either express or implied. See the License for the

// specific language governing permissions and limitations under the License.

#include <stdio.h>

int main()

printf("Hello World!!!!\n");

return 0;

```

- ZIP file from github includes:

- RTL Code

- Testbench

- Example C code

- Makefile

```

# CMAKE generated file: DO NOT EDIT!

# Generated by "Unix Makefiles" Generator, CMake Version 3.5

# Default target executed when no arguments are given to make.

default target: all

.PHONY : default target

# Allow only one "make -f Makefile2" at a time, but pass parallelism.

.NOTPARALLEL:

# Special targets provided by cmake.

# Disable implicit rules so canonical targets will work.

.SUFFIXES:

# Remove some rules from gmake that .SUFFIXES does not remove.

SUFFIXES =

.SUFFIXES: .hpux make needs suffix list

# Suppress display of executed commands.

$(VERBOSE).SILENT:

# A target that is always out of date.

cmake force:

.PHONY : cmake_force

```

## **Modelsim Simulation**

```

riscv define... VIPackage

Package

apu_core_package

apu_core_p... VIPackage

Package

riscv core sv unit

riscv core ... VIPackage

Package

riscv if stage sv unit

riscv if sta... VIPackage

Package

riscy compressed decoder sy unit

riscv comp... VIPackage

Package

riscv id stage sv unit

riscv id sta... VIPackage

Package

iccy decoder sy unit

riscy decod V/IPackage

Package

Memory List

🏿 🌉 sim 🗴

Transcript

Time: U ps Iteration: U instance: /tb File: /nome/adi/pulpino/vsim/..//tb/tb.sv

VSIM 2> run -all

# ** Warning: NUMERIC STD."=": metavalue detected, returning FALSE

Time: 0 ps Iteration: 0 Instance: /tb/top_i/peripherals_i/apb_uart_i/UART_RXFF

# ** Warning: NUMERIC STD."=": metavalue detected, returning FALSE

Time: 0 ps Iteration: 0 Instance: /tb/top i/peripherals i/apb uart i/UART TXFF

# Using MEMLOAD method: PRELOAD

ri5cy core

# Using

# [SPI] Enabling QPI mode

# [adv dbq if] AXI4 WRITE

32 burst @1a107008 for

4 bytes.

# Preloading memory

# Preloading instruction memory from slm files/l2 stim.slm

# Preloading data memory from slm_files/tcdm_bank0.slm

trace core 00 0.log

RX string: Hello World!!!!!

# [SPI] Test OK

: /home/adi/pulpino/vsim/..//tb/tb.sv(379)

# ** Note: $stop

Time: 261040 ns Iteration: 0 Instance: /tb

# Break in Module tb at /home/adi/pulpino/vsim/..//tb/tb.sv line 379

```

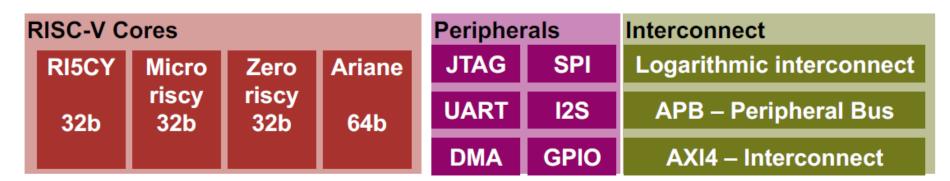

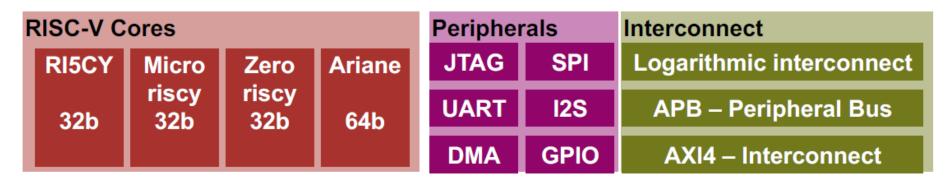

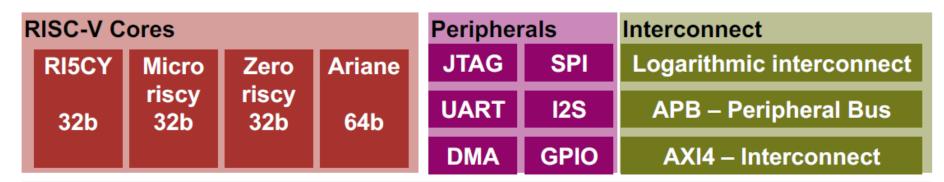

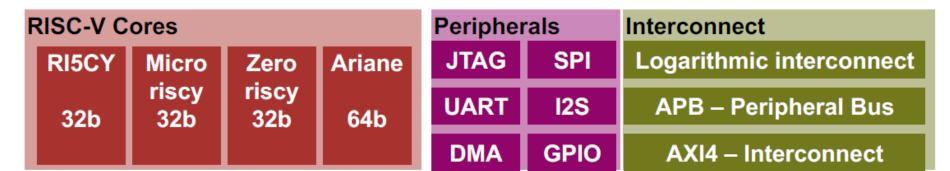

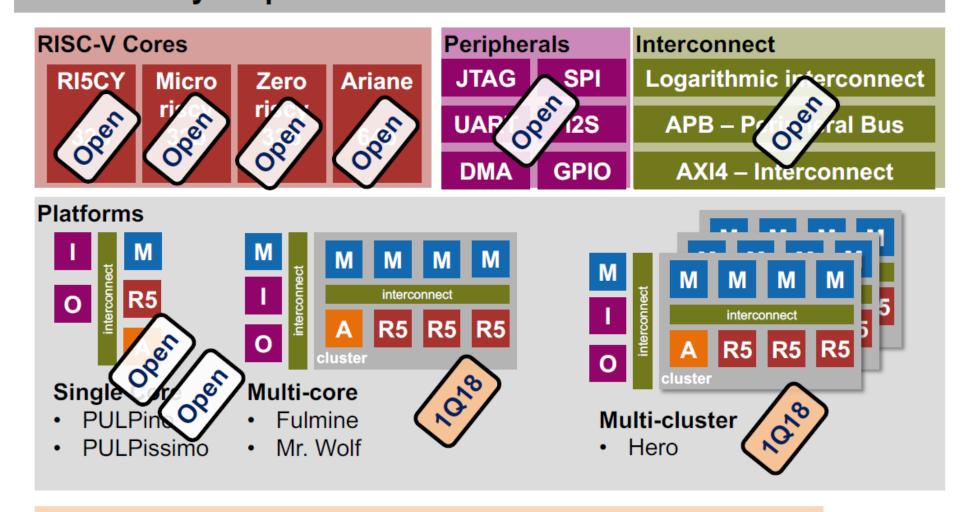

## The PULP family explained

Peripherals **RISC-V Cores** Interconnect **Platforms**

**Accelerators**

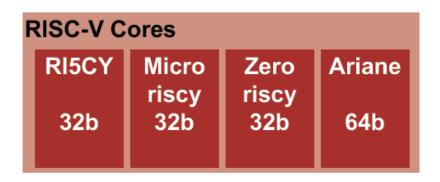

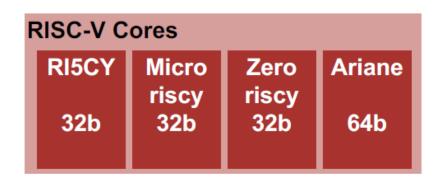

## We have developed several optimized RISC-V cores

## We have also been working on hardware accelerators

## We have our own peripherals and interconnect solutions

## By combining these components we get PULP platforms

#### **Platforms**

#### **Single Core**

- PULPino

- PULPissimo

#### **Accelerators**

HWCE (convolution)

Neurostream (ML)

HWCrypt (crypto)

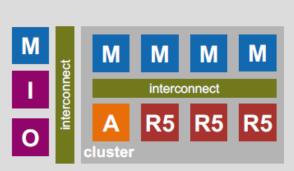

## Our main research is on Near-Threshold Multi-Core Systems

#### **Platforms**

#### **Single Core**

- PULPino

- PULPissimo

#### Multi-core

- Fulmine

- Mr. Wolf

#### **Accelerators**

HWCE (convolution)

Neurostream (ML)

HWCrypt (crypto)

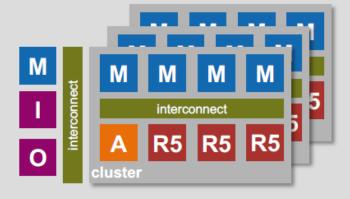

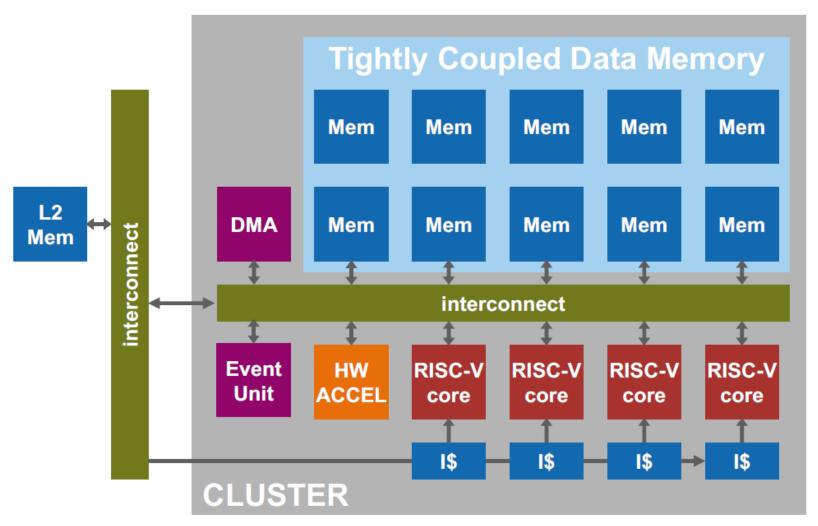

## Finally for HPC applications we have multi-cluster systems

#### **Platforms**

#### **Single Core**

- PULPino

- PULPissimo

#### Multi-core

- Fulmine

- Mr. Wolf

#### Multi-cluster

Hero

### IOT

#### **Accelerators**

HWCE (convolution)

Neurostream (ML)

HWCrypt (crypto)

### Eventually we plan to release ALL we did on PULP

#### **Accelerators**

HWCE (convolution)

Neurostream (ML)

HWCrypt (crypto)

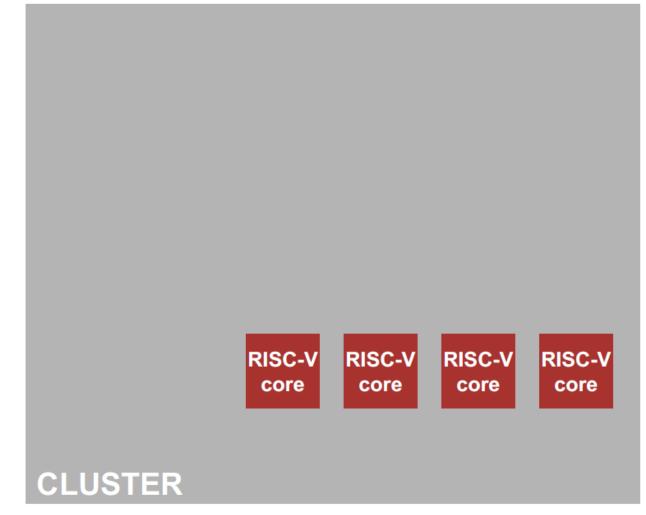

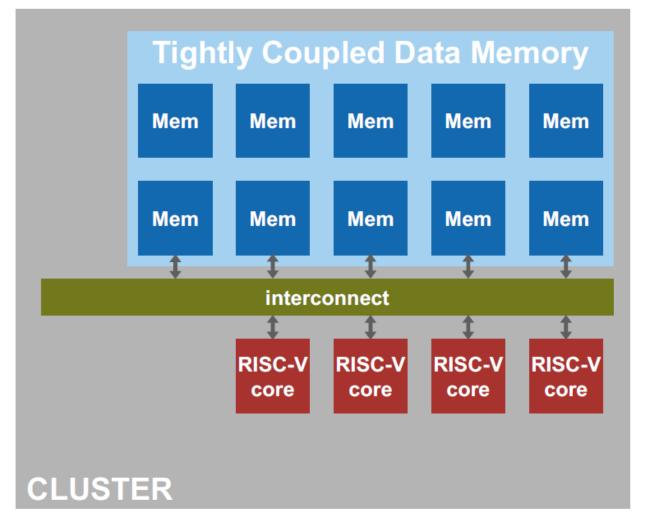

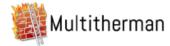

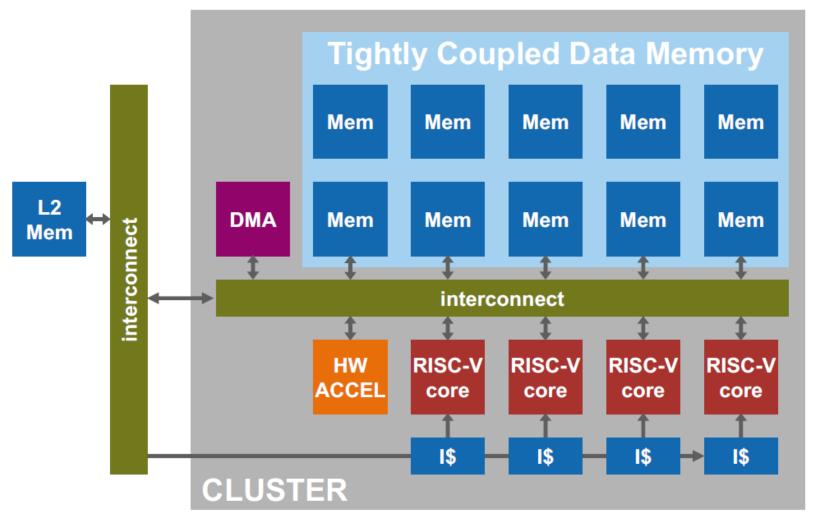

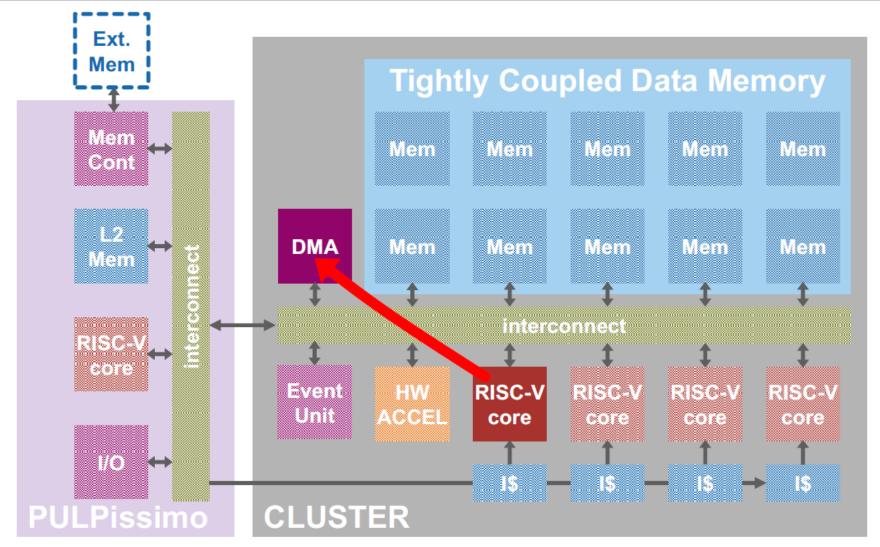

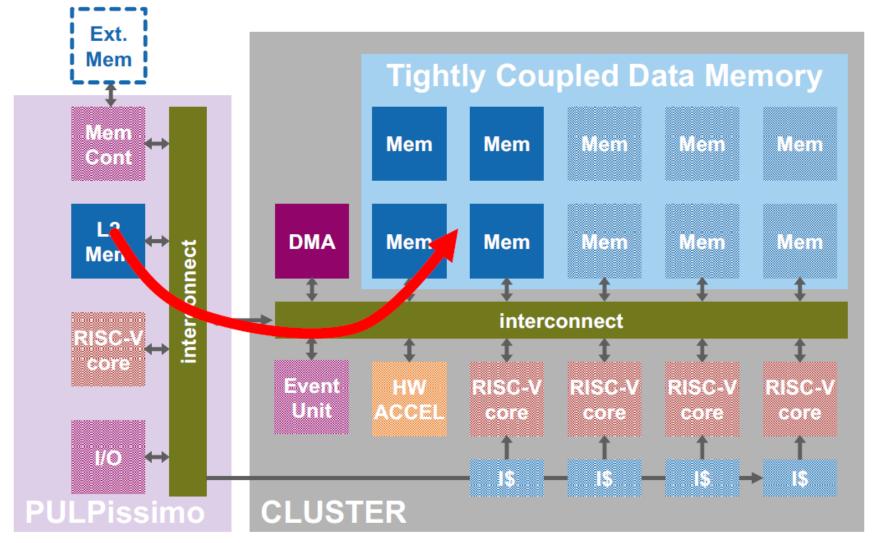

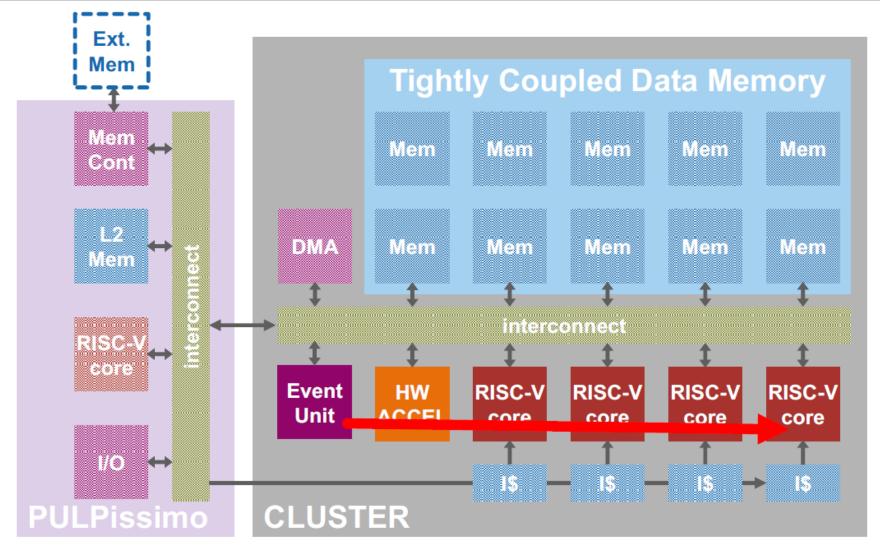

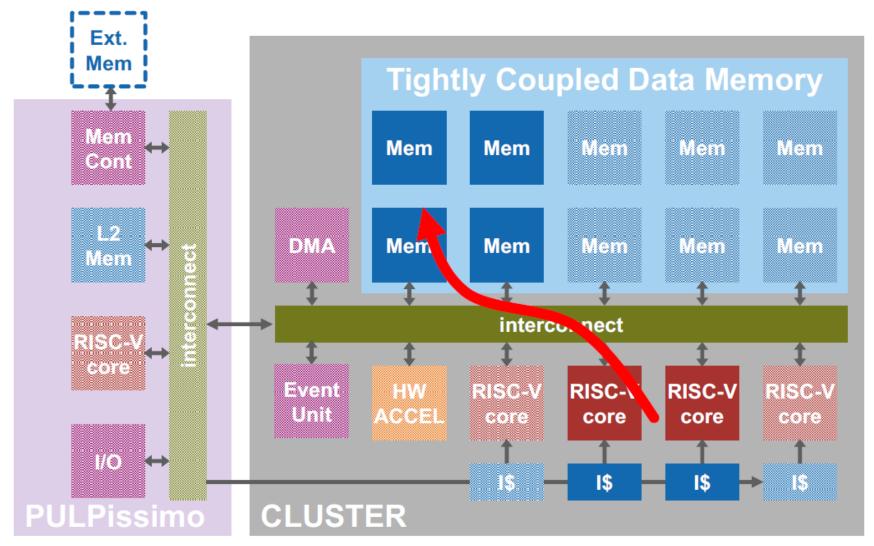

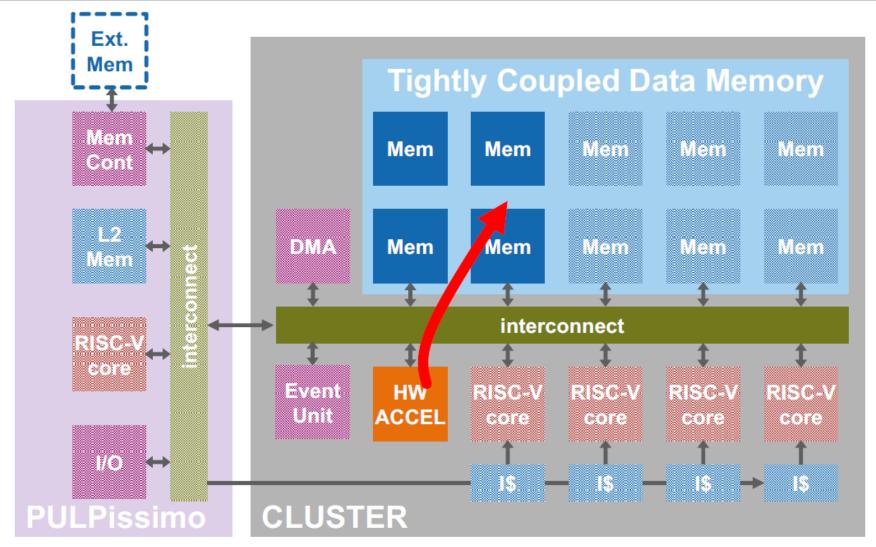

## PULP cluster contains multiple RISC-V cores

## All cores can access all memory banks in the cluster

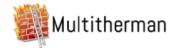

## Data is copied from a higher level through DMA

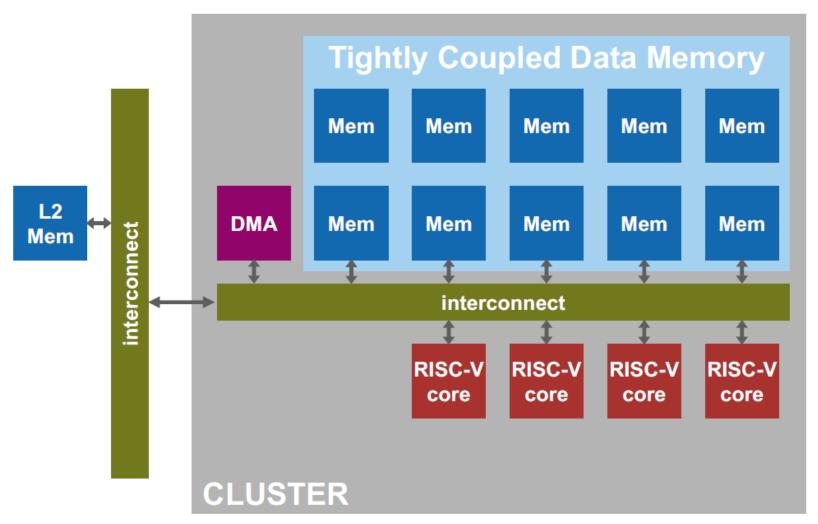

### There is a (shared) instruction cache that fetches from L2

#### Hardware Accelerators can be added to the cluster

## Event unit to manage resources (fast sleep/wakeup)

## An additional microcontroller system (PULPissimo) for I/O

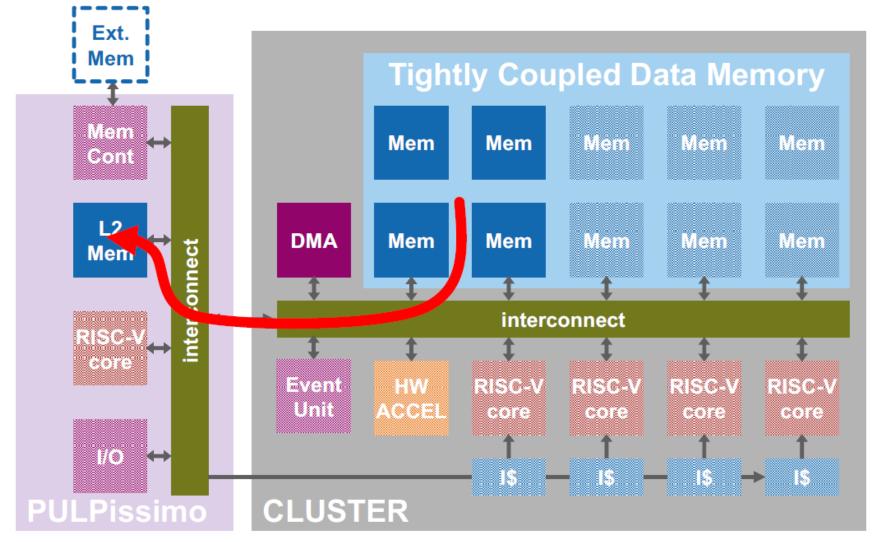

#### How do we work: Initiate a DMA transfer

## Data copied from L2 into TCDM

## Once data is transferred, event unit notifies cores/accel

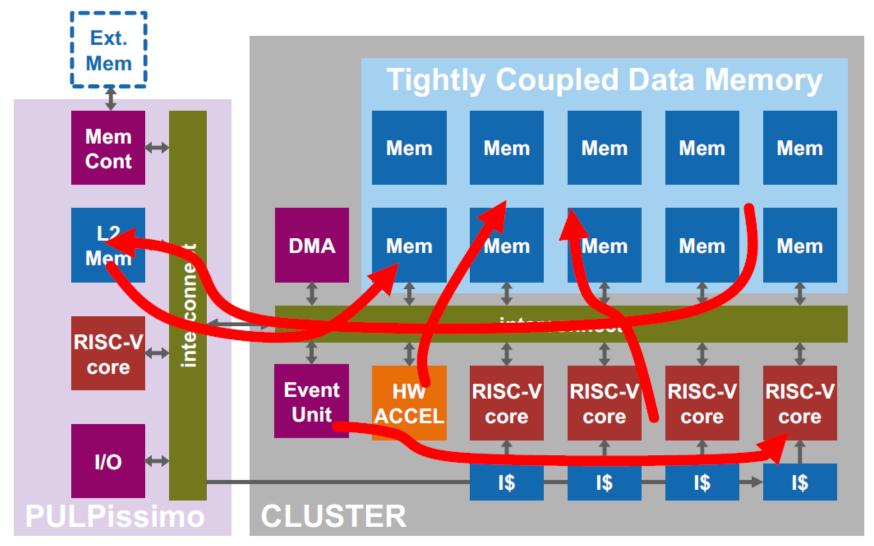

#### Cores can work on the data transferred

### Or accelerators

## Once our work is done, DMA copies data away

#### DMA data copies and processing actually work in parallel

## RISC-V cores under development

| 32 bit        |                               |                              |  |  |

|---------------|-------------------------------|------------------------------|--|--|

| Low Cost Core | Core with DSP enhancements    | Floating-point capable Core  |  |  |

| Zero-riscy    | - RI5CY                       | RI5CY + FPU                  |  |  |

| RV32-ICM      | RV32-ICMX                     | <ul><li>RV32-ICMFX</li></ul> |  |  |

| Micro-riscy   | <ul><li>SIMD</li></ul>        |                              |  |  |

| RV32-CE       | <ul><li>HW loops</li></ul>    |                              |  |  |

|               | Bit Man                       |                              |  |  |

|               | <ul><li>Fixed point</li></ul> |                              |  |  |

|               |                               |                              |  |  |

#### 64 bit Linux capable Core

- Ariane

- RV64-IC(MA)

- Full privileged specification

- Integer instructions (frozen)

Reduced number of registers

Multiplication and Division (frozen)

Atomic instructions (frozen)

Single-Precision Floating-Point (frozen)

Double-Precision Floating-Point (frozen)

Compressed Instructions (frozen)

Non Standard Extensions

## PULP Open-Source Releases and External Contributions

February 2016

First release of PUL

First release of **PULPino**, our single-core microcontroller

May 2016

Toolchain and compiler for our RISC-V implementation (RI5CY), DSP extensions

August 2017

PULPino updates, new cores Zero-riscy and Micro-riscy, FPU, toolchain updates

February 2018

PULPissimo, ARIANE, PULP

A bit later in 2018 PULP, HERO

#### **PULP Success**

- Many companies (we know of) are actively using PULP

- They value that it is silicon proven

- They like that it uses a permissive open source license

|   | GreenWaves Technologies    | NXP              |

|---|----------------------------|------------------|

|   | Dolphin                    | Shanghai Xidian  |

|   | IQ Analog (14nm chips)     | Technology       |

|   | Embecosm                   | SCS Zurich       |

|   | lowRISC                    | IMT technologies |

|   | Mentor Graphics            | Google           |

|   | Cadence Design Systems     | Microsemi        |

| 4 | ST Microelectronics (IT,F) | Arduino          |

|   | Micron                     | <br>RacylCs      |

|   | SIAE Microelectronica      |                  |

|   | Advanced Circuit Pursuit   |                  |

| Research Centers/Universities using PULP |                              |   |                       |  |  |

|------------------------------------------|------------------------------|---|-----------------------|--|--|

|                                          | Stanford                     | - | Zagreb HER            |  |  |

|                                          | Cambridge                    |   | Universita di Genova  |  |  |

|                                          | UCLA                         |   | Istanbul Technical U. |  |  |

|                                          | CEA/LETI                     |   | RWTH Aachen           |  |  |

|                                          | EPFL                         |   | Lund                  |  |  |

|                                          | National Chia Tung           |   | USI – Lugano          |  |  |

|                                          | University                   |   | Bar-Ilan              |  |  |

|                                          | Politecnico di Milano        |   | TU-Kaiserslautern     |  |  |

|                                          | Politecnico di Torino        |   | TU-Graz               |  |  |

|                                          | Universita Roma I            |   | UC San Diego          |  |  |

|                                          | Instituto Superior Tecnico – |   | CSEM                  |  |  |

|                                          | U. de Lisboa                 |   | IBM Research          |  |  |

|                                          | Fondazione Bruno Kessler     |   |                       |  |  |

|                                          |                              |   |                       |  |  |

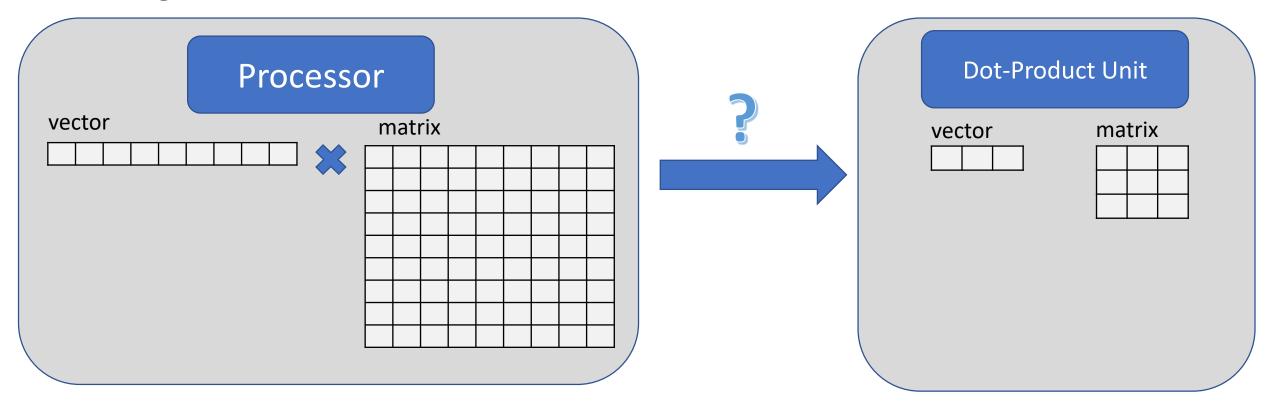

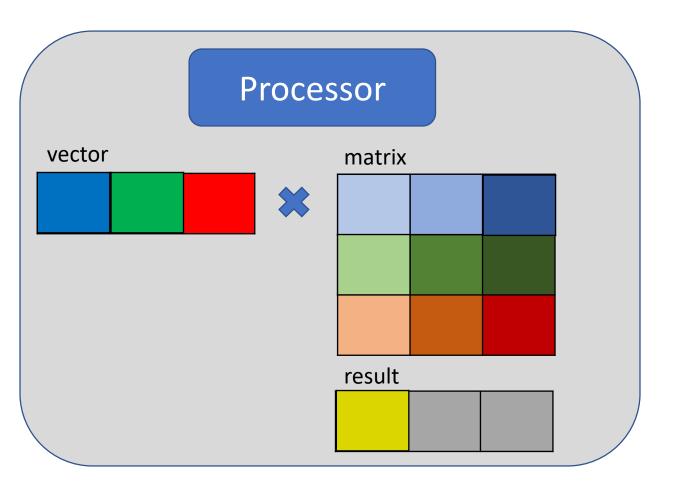

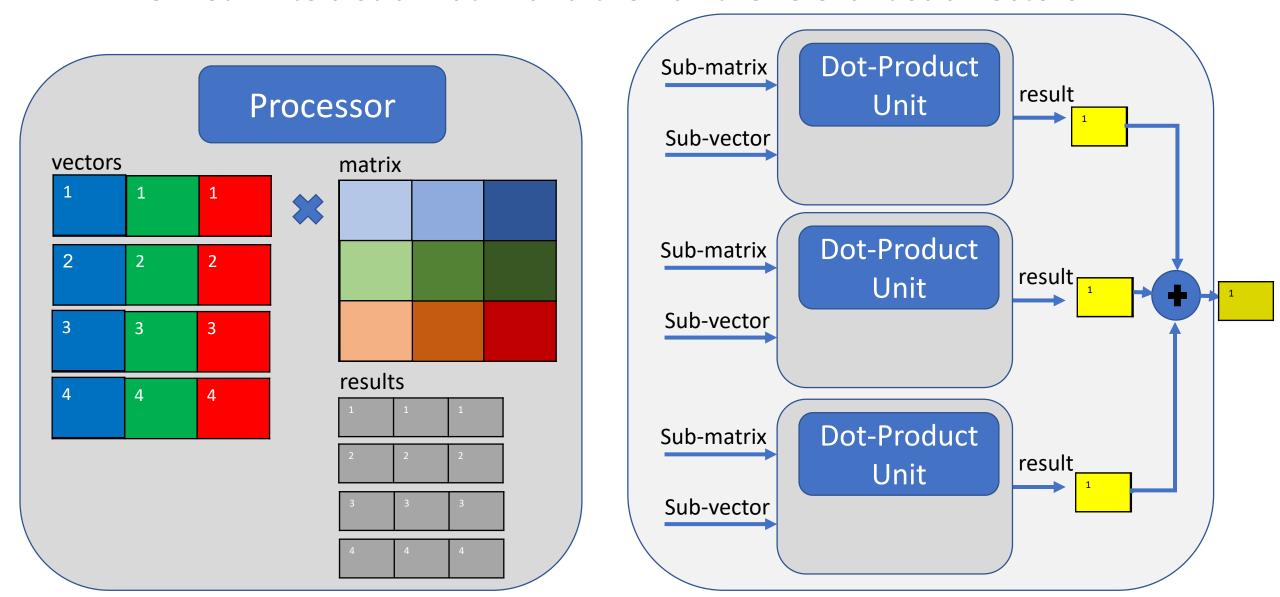

## A Few Words about My Project

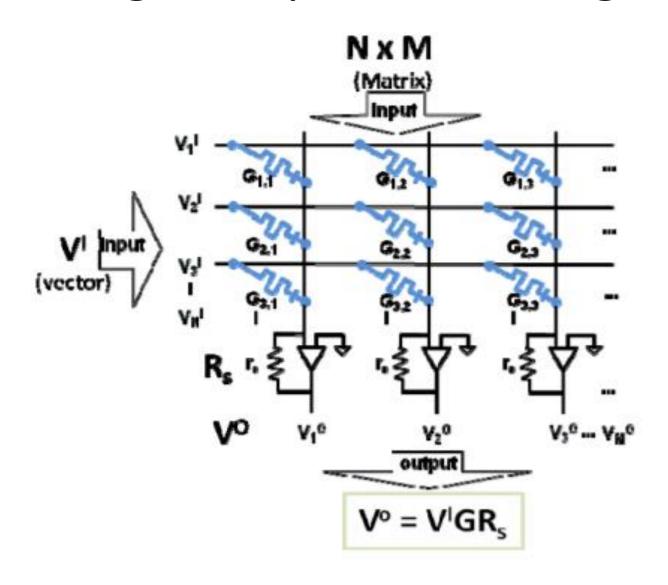

- Design new application-dedicated logic elements, that will be energy efficient, and integrate them in the PULP processor:

- A CCLO (Configurable Combinational Logic Operator) unit

- enables the realization of application specific operations and software customization. For example, LUTs

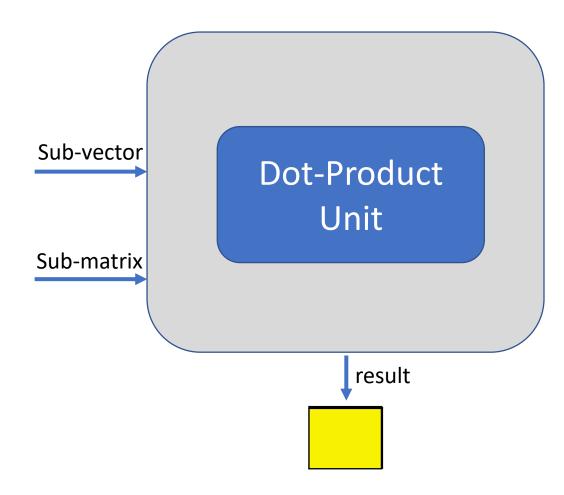

- A dot-product unit, which calculates matrix and vector multiplication

- Uses a memristors crossbar

- Useful for machine-learning applications

## Calculating Multiplication using a Crossbar

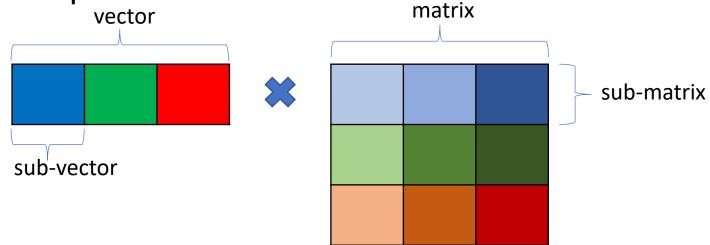

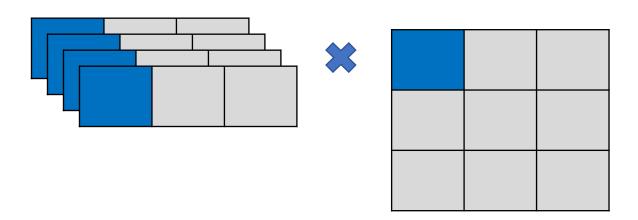

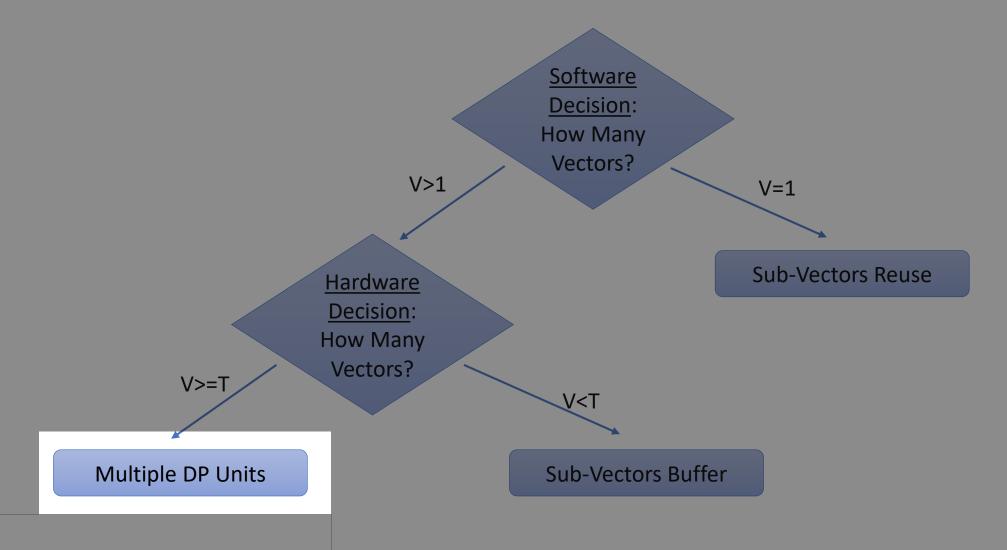

# The Problem: Multiplying Large Vector and Large Matrix

• The Dot-Product unit is not large enough to store large vectors and large matrices.

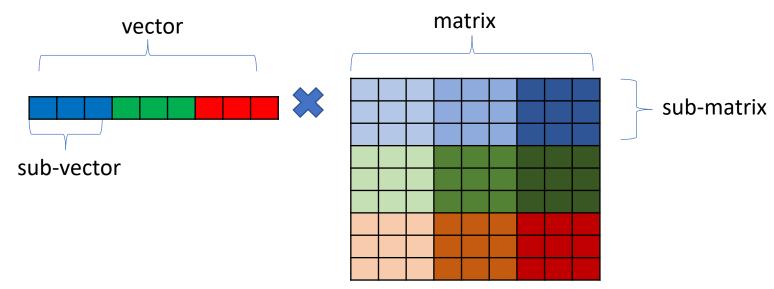

## The Solution: Dividing The Vector & Matrix

• Dividing the vector to sub-vectors, and the matrix to sub-matrices:

- The blue sub-matrices are multiplied by the blue sub-vector, the green ones with the green vector, etc.

- Additional calculations (summing the results) are performed in the processor.

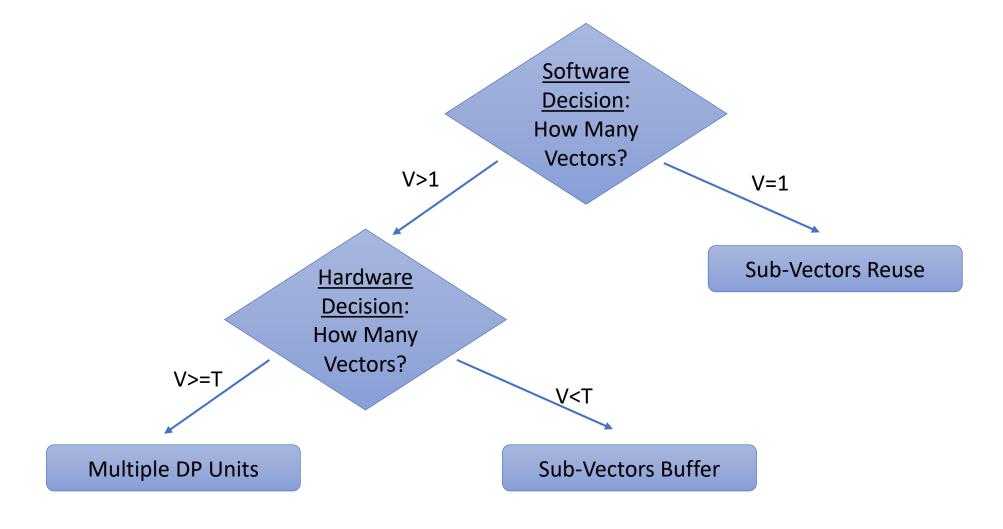

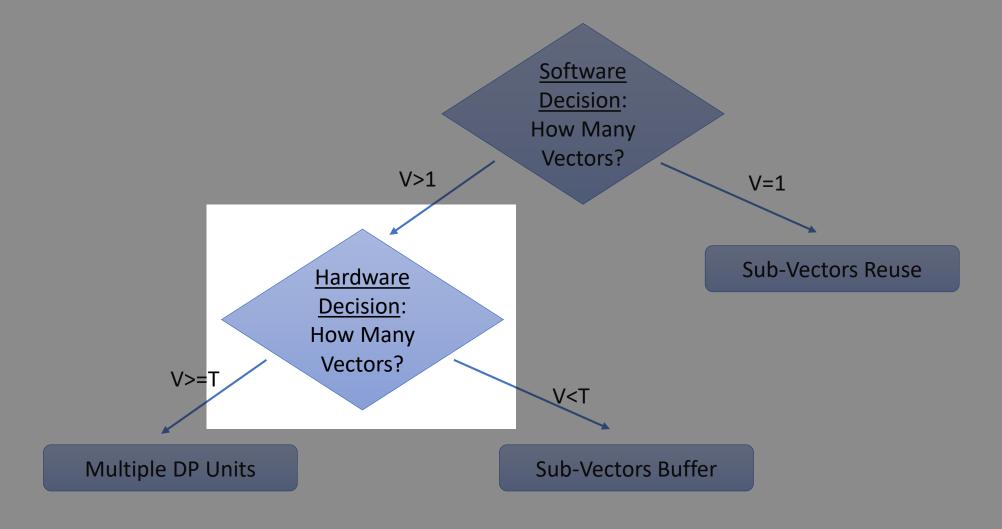

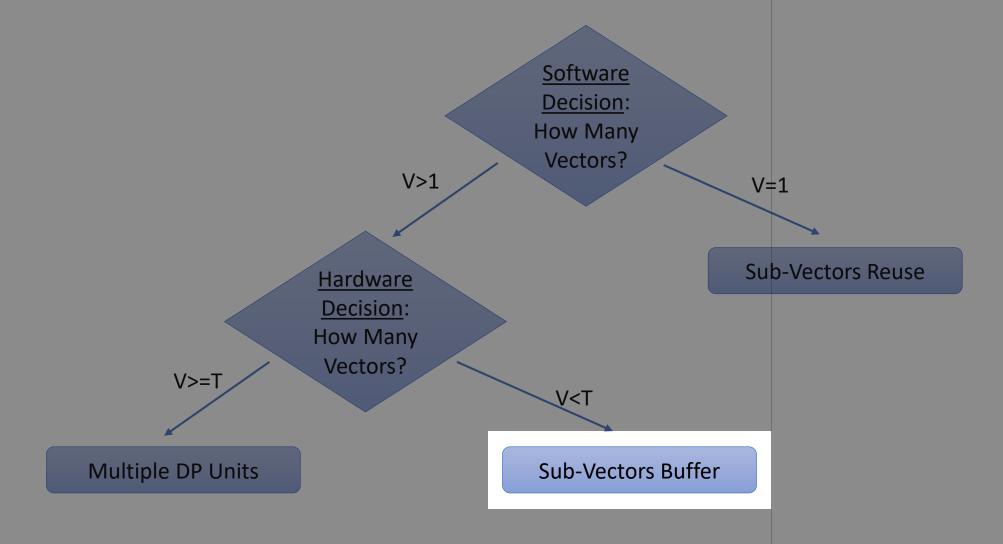

#### One Vector: Sub-Vectors Reuse

• A simple example:

- The blue sub-matrices are multiplied by the blue sub-vector, the green ones with the green vector, etc.

- Each sub-matrix is used once. Each sub-vector is used 3 times.

#### One Vector: Sub-Vectors Reuse

We first write a sub-vector and then all the relevant row submatrices:

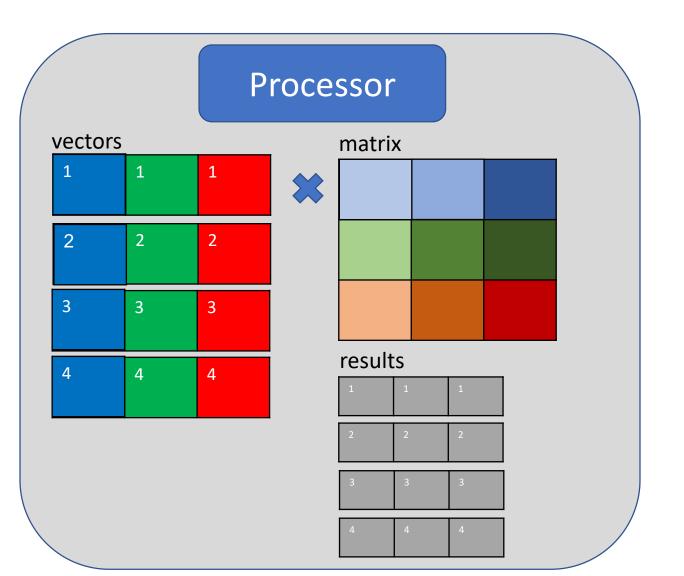

### Multiple Vectors: Sub-Matrices Reuse

- When having multiple vectors, each sub-matrix is used more than once.

- In the following example, the blue sub-matrix is multiplied by all the blue sub-vectors:

• Since matrices are larger than vectors, we'd rather reuse sub-matrices rather then reuse sub-vectors, like before.

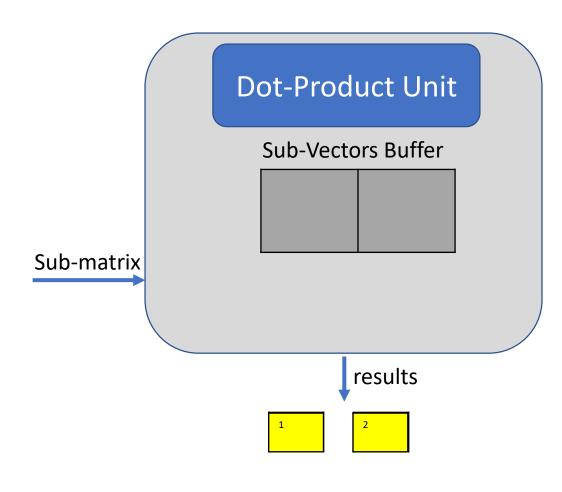

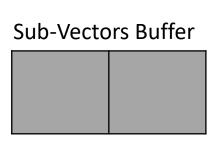

#### Sub-Vectors Buffer

• We first write a sub-matrix and then all the relevant sub-vectors:

#### Sub-Vectors Buffer - Issues

When the number of vectors isn't a multiplication of the buffer size, the last group of vectors will take only part of the buffer. The reused sub-vectors in the next sub-matrix are not sorted, therefore the results should be placed in the right location:

### Multiple DP Units

• We first write a sub-matrix and then all the relevant sub-vectors:

#### What's Next?

- Developing an accelerator "by the book"

- Using the accelerator DMA

- Cache prefetching

- Reducing the number of add cycles

- Real performance analysis

## Thank You!